Power ISA

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM. It was originally developed by IBM and the now-defunct Power.org industry group. Power ISA is an evolution of the PowerPC ISA, created by the mergers of the core PowerPC ISA and the optional Book E for embedded applications. The merger of these two components in 2006 was led by Power.org founders IBM and Freescale Semiconductor.

| Designer | |

|---|---|

| Bits | 32-bit/64-bit (32 → 64) |

| Introduced | 2006 |

| Version | 3.1 |

| Design | RISC |

| Type | Register–Register |

| Encoding | Fixed/Variable |

| Branching | Condition code |

| Endianness | Big/Bi |

| Extensions | AltiVec, PowerPC AS, APU, DSP, CBEA |

| Open | Yes, and royalty free |

| Registers | |

| |

Prior to version 3.0, the ISA is divided into several categories. Processors implement a set of these categories as required for their task. Different classes of processors are required to implement certain categories, for example a server-class processor includes the categories: Base, Server, Floating-Point, 64-Bit, etc. All processors implement the Base category.

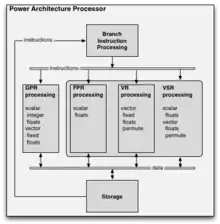

Power ISA is a RISC load/store architecture. It has multiple sets of registers:

- 32 × 32-bit or 64-bit general-purpose registers (GPRs) for integer operations.

- 64 × 128-bit vector scalar registers (VSRs) for vector operations and floating-point operations.

- 32 × 64-bit floating-point registers (FPRs) as part of the VSRs for floating-point operations.

- 32 × 128-bit vector registers (VRs) as part of the VSRs for vector operations.

- 8 × 4-bit condition register fields (CRs) for comparison and control flow.

- 11 special registers of various sizes: Counter Register (CTR), link register (LR), time base (TBU, TBL), alternate time base (ATBU, ATBL), accumulator (ACC), status registers (XER, FPSCR, VSCR, SPEFSCR).

Instructions up to version 3.0 have a length of 32 bits, with the exception of the VLE (variable-length encoding) subset that provides for higher code density for low-end embedded applications, and version 3.1 which introduced prefixing to create 64-bit instructions. Most instructions are triadic, i.e. have two source operands and one destination. Single- and double-precision IEEE-754 compliant floating-point operations are supported, including additional fused multiply–add (FMA) and decimal floating-point instructions. There are provisions for single instruction, multiple data (SIMD) operations on integer and floating-point data on up to 16 elements in one instruction.

Power ISA has support for Harvard cache, i.e. split data and instruction caches, and support for unified caches. Memory operations are strictly load/store, but allow for out-of-order execution. There is also support for both big and little-endian addressing with separate categories for moded and per-page endianness, and support for both 32-bit and 64-bit addressing.

Different modes of operation include user, supervisor and hypervisor.

Categories

- Base – Most of Book I and Book II

- Server – Book III-S

- Embedded – Book III-E

- Misc – floating point, vector, signal processing, cache locking, decimal floating point, etc.

Books

The Power ISA specification is divided into five parts, called "books":

- Book I – User Instruction Set Architecture covers the base instruction set available to the application programmer. Memory reference, flow control, Integer, floating point, numeric acceleration, application-level programming. It includes chapters regarding auxiliary processing units like digital signal processors (DSPs) and the AltiVec extension.

- Book II – Virtual Environment Architecture defines the storage model available to the application programmer, including timing, synchronization, cache management, storage features, byte ordering.

- Book III – Operating Environment Architecture includes exceptions, interrupts, memory management, debug facilities and special control functions. It is divided into two parts.

- Book III-S – Defines the supervisor instructions used for general-purpose/server implementations. It is mainly the contents of the Book III of the former PowerPC ISA.

- Book III-E – Defines the supervisor instructions used for embedded applications. It is derived from the former PowerPC Book E.

- Book VLE – Variable Length Encoded Instruction Architecture defines alternative instructions and definitions from Books I–III, intended for higher instruction density and very-low-end applications. They use 16-bit instructions and big-endian byte ordering.

Compliancy

New in version 3 of the Power ISA is that you don't have to implement the entire specification to be compliant. The sprawl of instructions and technologies has made the complete specification unwieldy, so the OpenPOWER Foundation have decided to enabled tiered compliancy.

These levels include optional and mandatory requirements, however one common misunderstanding is that there is nothing stopping an implementation from being compliant at a lower level but having additional selected functions from higher levels and custom extensions. It is however recommended that an option be provided to disable any added functions beyond the design's declared subset level.

A design must be compliant at its declared subset level to make use of the Foundation's protection regarding use of intellectual property, be it patents or trademarks. This is explained in the OpenPOWER EULA.[1]

A compliant design must:[2]

- Support the Base architecture

- And support at least one of the subsets

- SFS – Scalar Fixed-point Subset. 129 instructions. Basic fixed point and load/store instructions, which is really the Base architecture.

- SFFS – Scalar Fixed-point + Floating-point Subset. 214 instructions. Adding floating-point operations to the Base.

- LCS – Linux Compliancy Subset. 962 instructions. Intended for server grade Linux, adding features like 64-bit, optional SIMD/VSX, Radix MMU, little-endian mode and hypervisor support.

- ACS – AIX Compliancy Subset. 1099 instructions. Intended to run AIX, adding features like decimal and quad-precision floating point, big-endian mode and symmetric multiprocessing.

- May include any of the features of the LCS and ACS as Optional or pick from the Always Optional features like matrix math and power management.

- Optional features, if chosen, must be implemented in their entirety (partial implementation of an Optional feature is not permitted)

- May include Custom extensions, specific to the implementation, implemented in the Architecture Sandbox.

If the extension is general-purpose enough, the OpenPOWER Foundation asks that implementors submit it as a Request for Comments (RFC) to the OpenPOWER ISA Workgroup. Note that it is not strictly necessary to join the OpenPOWER Foundation to submit RFCs.[3]

- Much may be implemented in either hardware or firmware.

EABI and Linux Compliancy discrepancy

The EABI specifications predate the announcement and creation of the Compliancy subsets.

Regarding the Linux Compliancy subset having VSX (SIMD) optional: in 2003–4, 64-bit EABI v1.9 made SIMD optional,[4] but in July 2015, to improve performance for IBM POWER9 systems, SIMD was made mandatory in EABI v2.0.[5] This discrepancy between SIMD being optional in the Linux Compliancy level but mandatory in EABI v2.0 cannot be rectified without considerable effort: backwards incompatibility for Linux distributions is not a viable option. At present this leaves new OpenPOWER implementors wishing to run standard Linux distributions having to implement a massive 962 instructions. By contrast, RISC-V RV64GC, the minimum to run Linux, requires only 165.[6]

Specifications

Power ISA v.2.03

The specification for Power ISA v.2.03[7] is based on the former PowerPC ISA v.2.02[8] in POWER5+ and the Book E[9] extension of the PowerPC specification. The Book I included five new chapters regarding auxiliary processing units like DSPs and the AltiVec extension.

- Compliant cores

Power ISA v.2.04

The specification for Power ISA v.2.04[10] was finalized in June 2007. It is based on Power ISA v.2.03 and includes changes primarily to the Book III-S part regarding virtualization, hypervisor functions, logical partitioning and virtual page handling.

- Compliant cores

Power ISA v.2.05

The specification for Power ISA v.2.05[11] was released in December 2007. It is based on Power ISA v.2.04 and includes changes primarily to Book I and Book III-S, including significant enhancements such as decimal arithmetic (Category: Decimal Floating-Point in Book I) and server hypervisor improvements.

- Compliant cores

- All cores that comply with prior versions of the Power ISA

- POWER6

- PowerPC 476

Power ISA v.2.06

The specification for Power ISA v.2.06[12] was released in February 2009, and revised in July 2010.[13] It is based on Power ISA v.2.05 and includes extensions for the POWER7 processor and e500-mc core. One significant new feature is vector-scalar floating-point instructions (VSX).[14] Book III-E also includes significant enhancement for the embedded specification regarding hypervisor and virtualisation on single and multi core implementations.

The spec was revised in November 2010 to the Power ISA v.2.06 revision B spec, enhancing virtualization features.[13][15]

- Compliant cores

Power ISA v.2.07

The specification for Power ISA v.2.07[16] was released in May 2013. It is based on Power ISA v.2.06 and includes major enhancements to logical partition functions, transactional memory, expanded performance monitoring, new storage control features, additions to the VMX and VSX vector facilities (VSX-2), along with AES[16]: 257 [17] and Galois Counter Mode (GCM), SHA-224, SHA-256,[16]: 258 SHA-384 and SHA-512[16]: 258 (SHA-2) cryptographic extensions and cyclic redundancy check (CRC) algorithms.[18]

The spec was revised in April 2015 to the Power ISA v.2.07 B spec.[19][20]

- Compliant cores

Power ISA v.3.0

The specification for Power ISA v.3.0[21][22] was released in November 2015. It is the first to come out after the founding of the OpenPOWER Foundation and includes enhancements for a broad spectrum of workloads and removes the server and embedded categories while retaining backwards compatibility and adds support for VSX-3 instructions. New functions include 128-bit quad-precision floating-point operations, a random number generator, hardware-assisted garbage collection and hardware-enforced trusted computing.

The spec was revised in March 2017 to the Power ISA v.3.0 B spec,[19][23] and revised again to v3.0C in May 2020.[19][24][25] One major change from v3.0 to v3.0B is the removal of support for hardware assisted garbage collection. The key difference between v3.0B and v3.0C is that the Compliancy Levels listed in v3.1 were also added to v3.0C.

- Compliant cores

- All cores that comply with prior versions of the Power ISA

- POWER9[26]

- OpenPOWER Microwatt

- Libre-SOC is aiming for Embedded FP compliancy with Power ISA 3.0 only

Power ISA v.3.1

The specification for Power ISA v.3.1[19][27] was released in May 2020. Mainly giving support for new functions introduced in Power10, but also includes the notion of optionality to the PowerISA specification. Instructions can now be eight bytes long, "prefixed instructions", compared to the usual four byte "word instructions". A lot of new functions to SIMD and VSX instructions are also added. VSX and the SVP64 extension provide hardware support for 16-bit half precision floats.[28][29]

One key benefit of the new 64-bit prefixed instructions is the extension of immediates in branches to 34-bit.

The spec was revised in September 2021 to the Power ISA v.3.1B spec.[19][30]

- Compliant cores

See also

References

- Final draft of Power ISA EULA

- The Open Power ISA: Architecture Compliancy and Future Foundations

- Section 2.2 of OPF Power ISA EULA

- ELF PP64 ABI

- OpenPOWER EABI v2

- Page 18 RISC-V "green card"

- "Power ISA v.2.03" (PDF). Power.org. 2006-09-29. Archived from the original (PDF) on 2011-07-27.

- "PowerPC Architecture Book, Version 2.02". IBM. 2005-02-24. Archived from the original on 2007-10-18. Retrieved 2007-03-16.

- "PowerPC Book E v.1.0" (PDF). IBM. 2002-05-07. Archived (PDF) from the original on 2018-03-10. Retrieved 2007-03-16.

- "Power ISA Version 2.04" (PDF). Power.org. 2007-06-12. Archived from the original (PDF) on 2007-09-27. Retrieved 2007-06-14.

- "Power ISA Version 2.05". Power.org. 2007-10-23. Archived from the original on 2012-11-24. Retrieved 2007-12-18.

- "Power.org Debuts Specification Advances and New Services At Power Architecture Developer Conference" (Press release). Power.org. 2007-09-24. Archived from the original on 2007-10-12. Retrieved 2007-09-24.

- "Power ISA Version 2.06 Revision B". Power.org. 2010-07-23. Archived from the original on 2012-11-24. Retrieved 2011-02-12.

- "Workload acceleration with the IBM POWER vector-scalar architecture". IBM. 2016-03-01. Retrieved 2017-05-02.

- "Power ISA 2.06 Rev. B enables full hardware virtualization for embedded space". EETimes. 2010-11-03. Retrieved 2011-06-08.

- "Power ISA Version 2.07" (PDF). Power.org. 2013-05-15. Retrieved 2015-05-23.

- Barbosa, Leonidas (2014-09-21). "POWER8 in-core cryptography". IBM.

- Performance Optimization and Tuning Techniques for IBM Power Systems Processors Including IBM POWER8. IBM. August 2015. p. 48. ISBN 9780738440927.

- "Instruction Set Architecture". OpenPOWER Foundation.

- "Power ISA Version 2.07 B". Power.org. 2015-04-09. Retrieved 2023-02-23.

- Announcing a New Era of Openness with Power 3.0

- "Power ISA Version 3.0". openpowerfoundation.org. 2016-11-30. Retrieved 2017-01-06.

- "Power ISA Version 3.0 B". IBM. 2017-03-29. Retrieved 2023-02-23.

- "Power ISA Version 3.0 C". OpenPOWER Foundation. 2020-05-01. Retrieved 2023-02-23.

- list of Power ISA specifications

- [PATCH, COMMITTED] Add full Power ISA 3.0 / POWER9 binutils support

- "Power ISA Version 3.1". OpenPOWER Foundation. 2020-05-01. Retrieved 2023-02-23.

- "OPF_PowerISA_v3.1B.pdf". OpenPOWER Files. OpenPOWER Foundation. Retrieved 2023-07-02.

- "ls005.xlen.mdwn". libre-soc.org Git. Retrieved 2023-07-02.

- "Power ISA Version 3.1B". OpenPOWER Foundation. 2021-09-14. Retrieved 2023-02-23.

- Seo, Carlos Eduardo (2020-05-12). "We released the Instruction Set Architecture for POWER10. Power ISA v3.1 is available at the IBM Portal for OpenPOWER". twitter.com. Retrieved 2020-05-23.