Package on a package

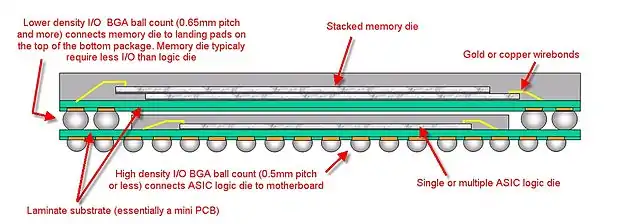

Package on a package (PoP) is an integrated circuit packaging method to vertically combine discrete logic and memory ball grid array (BGA) packages. Two or more packages are installed atop each other, i.e. stacked, with a standard interface to route signals between them. This allows higher component density in devices, such as mobile phones, personal digital assistants (PDA), and digital cameras, at the cost of slightly higher height requirements. Stacks with more than 2 packages are uncommon, due to heat dissipation considerations.

Configuration

Two widely used configurations exist for PoP:

- Pure memory stacking: two or more memory only packages are stacked on each other

- Mixed logic-memory stacking: logic (CPU) package on the bottom, memory package on top. For example, the bottom could be a system on a chip (SoC) for a mobile phone. The logic package is on the bottom because it needs many more BGA connections to the motherboard.

During PCB assembly, the bottom package of a PoP stack is placed directly on the PCB, and the other package(s) of the stack are stacked on top. The packages of a PoP stack become attached to each other (and to the PCB) during reflow soldering.

Benefits

The package on a package technique tries to combine the benefits of traditional packaging with the benefits of die-stacking techniques, while avoiding their drawbacks.

Traditional packaging places each die in its own package, a package designed for normal PCB assembly techniques that place each package directly on the PCB side-by-side. The 3D die-stacking system in package (SiP) techniques stacks multiple die in a single package, which has several advantages and also some disadvantages compared to traditional PCB assembly.

In embedded PoP techniques, chips are embedded in a substrate on the bottom of the package. This PoP technology enables smaller packages with shorter electrical connections and is supported by companies such as Advanced Semiconductor Engineering (ASE).[1]

Advantages over traditional isolated-chip packaging

The most obvious benefit is motherboard space savings. PoP uses much less PCB area, almost as little as stacked-die packages.

Electrically, PoP offers benefits by minimizing track length between different interoperating parts, such as a controller and memory. This yields better electrical performance of devices, since shorter routing of interconnections between circuits yields faster signal propagation and reduced noise and cross-talk.

Advantages over chip stacking

There are several key differences between stacked-die and stacked-package products.

The main financial benefit of package on a package is that the memory device is decoupled from the logic device. Therefore this gives PoP all the same advantages that traditional packaging has over stacked-die products:

- The memory package can be tested separately from the logic package

- Only "known good" packages are used in final assembly (if the memory is bad only the memory is discarded and so on). Compare this to stacked-die packages where the entire set is useless and rejected if either the memory or logic is bad.

- The end user (such as makers of mobile phones or digital cameras) controls the logistics. This means memory from different suppliers can be used at different times without changing the logic. The memory becomes a commodity to be sourced from the lowest cost supplier. This trait is also a benefit compared to PiP (package in package) which requires a specific memory device to be designed in and sourced upstream of the end user.

- Any mechanically mating top package can be used. For a low-end phone, a smaller memory configuration may be used on the top package. For a high-end phone, more memory could be used with the same bottom package.[2] This simplifies inventory control by the OEM. For a stacked-die package or even PiP (package in package), the exact memory configuration must be known weeks or months in advance.

- Because the memory only comes into the mix at final assembly, there is no reason for logic suppliers to source any memory. With a stacked-die device, the logic provider must buy wafers of memory from a memory supplier.

JEDEC standardization

- JEDEC JC-11 committee deals with package outline drawing standards related to the bottom PoP package. See documents MO-266A and JEDEC publication 95, Design Guide 4.22.

- JEDEC JC-63 committee deals with top (memory) PoP package pinout standardization. See JEDEC Standard No. 21-C, Page 3.12.2 – 1

Other names

Package on a package is also known by other names:

- PoP: refers to the combined top and bottom packages

- PoPt: refers to the top package

- PoPb: refers to the bottom package

- PSvfBGA: refers to the bottom package: Package Stackable Very thin Fine pitch Ball Grid Array[3]

- PSfcCSP: refers to the bottom package: Package Stackable Flip Chip Chip Scale Package

History

In 2001, a Toshiba research team including T. Imoto, M. Matsui and C. Takubo developed a "System Block Module" wafer bonding process for manufacturing 3D integrated circuit (3D IC) packages.[4][5] The earliest known commercial use of a 3D package-on-package chip was in Sony's PlayStation Portable (PSP) handheld game console, released in 2004. The PSP hardware includes eDRAM (embedded DRAM) memory manufactured by Toshiba in a 3D package chip with two dies stacked vertically.[6] Toshiba called it "semi-embedded DRAM" at the time, before later calling it a stacked "chip-on-chip" (CoC) solution.[6][7]

In April 2007, Toshiba commercialized an eight-layer 3D chip package, the 16 GB THGAM embedded NAND flash memory chip, which was manufactured with eight stacked 2 GB NAND flash chips.[8] The same month, U.S. Patent 7,923,830 ("Package-on-package secure module having anti-tamper mesh in the substrate of the upper package") was filed by Steven M. Pope and Ruben C. Zeta of Maxim Integrated.[9] In September 2007, Hynix Semiconductor introduced 24-layer 3D packaging technology, with a 16 GB flash memory chip that was manufactured with 24 stacked NAND flash chips using a wafer bonding process.[10]

References

- LaPedus, Mark (2014-06-19). "Mobile Packaging Market Heats Up". Semiconductor Engineering. Retrieved 2016-04-28.

- Thomas, Glen. "Package-on-Package Flux". Indium Corporation. Retrieved 2015-07-30.

- Amkor Technology. "Package on Package (PoP | PSfvBGA | PSfcCSP | TMV® PoP)". Retrieved 2015-07-30.

- Garrou, Philip (6 August 2008). "Introduction to 3D Integration". Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits (PDF). Wiley-VCH. p. 4. doi:10.1002/9783527623051.ch1. ISBN 9783527623051.

- Imoto, T.; Matsui, M.; Takubo, C.; Akejima, S.; Kariya, T.; Nishikawa, T.; Enomoto, R. (2001). "Development of 3-Dimensional Module Package, "System Block Module"". Electronic Components and Technology Conference. Institute of Electrical and Electronics Engineers (51): 552–7.

- James, Dick (2014). "3D ICs in the real world". 25th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC 2014). pp. 113–119. doi:10.1109/ASMC.2014.6846988. ISBN 978-1-4799-3944-2. S2CID 42565898.

- "System-in-Package (SiP)". Toshiba. Archived from the original on 3 April 2010. Retrieved 3 April 2010.

- "TOSHIBA COMMERCIALIZES INDUSTRY'S HIGHEST CAPACITY EMBEDDED NAND FLASH MEMORY FOR MOBILE CONSUMER PRODUCTS". Toshiba. April 17, 2007. Archived from the original on November 23, 2010. Retrieved 23 November 2010.

- "United States Patent US 7,923,830 B2" (PDF). 2011-04-12. Retrieved 2015-07-30.

- "Hynix Surprises NAND Chip Industry". Korea Times. 5 September 2007. Retrieved 8 July 2019.

Further reading

- Innovations push Package on Package into new markets, Flynn Carson, Semiconductor International, April 2010

- Practical Components PoP Samples and Test Boards (daisy chains)

- Package-on-Package: The Story Behind This Industry Hit (Semiconductor International, 2007-06-01)

- Package-on-package is killer app for handsets (EETimes Article July 2008)

- "POP" Goes the Future (Assembly Magazine, 2008-09-30)

- Package on Package: Top and Bottom PoP Technologies

- PoP Solder Balling (Circuits Assembly Magazine, December 2010)

- The BeagleBoard uses a PoP processor

- Killer app for cell handsets EETimes 2008-10-20

- TMV: An ‘Enabling’ Technology for Next-Gen PoP Requirements Semicon International 2008-11-04

- Rolling with Solder Balls (Circuits Assembly Magazine, October 2010)

- Don't Drown the Part! (Circuits Assembly Magazine, August 2010)

- POP (Package On Package): An Ems Perspective On Assembly, Rework And Reliability 2009-02-12

- Hamid Eslampour et al.Comparison of Advanced PoP Package Configurations, 2010 Electronic Components and Technology Conference (ECTC) Proceedings

- Package On Package Assembly Inspection & Quality Control Ebook, Bob Willis