POWER9

POWER9 is a family of superscalar, multithreading, multi-core microprocessors produced by IBM, based on the Power ISA. It was announced in August 2016.[2] The POWER9-based processors are being manufactured using a 14 nm FinFET process,[3] in 12- and 24-core versions, for scale out and scale up applications,[3] and possibly other variations, since the POWER9 architecture is open for licensing and modification by the OpenPOWER Foundation members.[5]

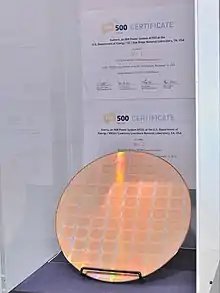

.jpg.webp) Technician holding a POWER9 processor | |

| General information | |

|---|---|

| Launched | 2017 |

| Designed by | IBM |

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | 4 GHz[1] |

| Cache | |

| L1 cache | 32+32 KiB per core[1] |

| L2 cache | 512 KiB per core[1] |

| L3 cache | 120 MiB per chip[1] |

| L4 cache | via Centaur[1] |

| Architecture and classification | |

| Technology node | 14 nm (FinFET) |

| Instruction set | Power ISA (Power ISA v.3.0) |

| Physical specifications | |

| Cores | |

| History | |

| Predecessor(s) | POWER8 |

| Successor(s) | Power10 |

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

| Cancelled in gray, historic in italic |

Summit, the fifth fastest supercomputer in the world (based on the Top500 list as of November 2022[6]), is based on POWER9, while also using Nvidia Tesla GPUs as accelerators.[7]

Design

Core

The POWER9 core comes in two variants, a four-way multithreaded one called SMT4 and an eight-way one called SMT8.[1] The SMT4- and SMT8-cores are similar, in that they consist of a number of so-called slices fed by common schedulers. A slice is a rudimentary 64-bit single-threaded processing core with load store unit (LSU), integer unit (ALU) and a vector scalar unit (VSU, doing SIMD and floating point). A super-slice is the combination of two slices. An SMT4-core consists of a 32 KiB L1 cache (1 KiB = 1024 bytes), a 32 KiB L1 data cache, an instruction fetch unit (IFU) and an instruction sequencing unit (ISU) which feeds two super-slices. An SMT8-core has two sets of L1 caches and, IFUs and ISUs to feed four super-slices. The result is that the 12-core and 24-core versions of POWER9 each consist of the same number of slices (96 each) and the same amount of L1 cache.

A POWER9 core, whether SMT4 or SMT8, has a 12-stage pipeline (five stages shorter than its predecessor, the POWER8), but aims to retain the clock frequency of around 4 GHz.[1] It will be the first to incorporate elements of the Power ISA v.3.0 that was released in December 2015, including the VSX-3 instructions.[8] The POWER9 design is made to be modular and used in more processor variants and used for licensing, on a different fabrication process than IBM's.[9] On chip are co-processors for compression and cryptography, as well as a large low-latency eDRAM L3 cache.[3]

The POWER9 comes with a new interrupt controller architecture called "eXternal Interrupt Virtualization Engine" (XIVE) which replaces a much simpler architecture that was used in POWER4 through POWER8. XIVE will also be used in Power10.[10][11][12]

Scale out / scale up

- IBM POWER9 SO – scale-out variant, optimized for dual socket computers with up to 120 GB/s bandwidth (1 GB = 1 billion bytes) to directly attached DDR4 memory[1][3][9] (targeted for release in 2017)

- IBM POWER9 SU – scale-up variant, optimized for four sockets or more, for large NUMA machines with up to 230 GB/s bandwidth to buffered memory[1][9] (uses "25.6 GHz" signaling with the PowerAXON 25 GT/sec Link interface[13])

Both POWER9 variants can ship in versions with some cores disabled due to yield reasons, as such Raptor Computing Systems first sold 4-core chips, and even IBM initially sold its AC922 systems with no more than 22-core chips, even though both types of chips have 24 cores on their dies.[14][4]

I/O

A lot of facilities are on-chip for helping with massive off-chip I/O performance:

- The SO variant has integrated DDR4 controllers for directly attached RAM, while the SU variant will use the off-chip Centaur architecture introduced with POWER8 to include high performance eDRAM L4 cache and memory controllers for DDR4 RAM.[1][3]

- The Bluelink interconnects for close attachment of graphics co-processors from Nvidia (over NVLink v.2) and OpenCAPI accelerators.[15]

- General purpose PCIe v.4 connections for attaching regular ASICs, FPGAs and other peripherals as well as CAPI 2.0 and CAPI 1.0 devices designed for POWER8.

- Multiprocessor (symmetric multiprocessor system) links to connect other POWER9 processors on the same motherboard, or in other closely attached enclosures.

Chip types

POWER9 chips can be made with two types of cores, and in a Scale Out or Scale Up configuration. POWER9 cores are either SMT4 or SMT8, with SMT8 cores intended for PowerVM systems, while the SMT4 cores are intended for PowerNV systems, which do not use PowerVM, and predominantly run Linux. With POWER9, chips made for Scale Out can support directly-attached memory, while Scale Up chips are intended for use with machines with more than two CPU sockets, and use buffered memory.[16][1]

| PowerNV | PowerVM | |

|---|---|---|

| 24 × SMT4 core | 12 × SMT8 core | |

| Scale Out | Nimbus | unknown |

| Scale Up | Cumulus |

Modules

The IBM Portal for OpenPOWER lists the three available modules for the Nimbus chip, although the Scale-Out SMT8 variant for PowerVM also uses the LaGrange module/socket:[17]

- Sforza – 50 mm × 50 mm, 4 DDR4, 48 PCIe lanes, 1 XBus 4B[18]

- Monza – 68.5 mm × 68.5 mm, 8 DDR4, 34 PCIe lanes, 1 XBus 4B, 48 OpenCAPI lanes[19]

- LaGrange – 68.5 mm × 68.5 mm, 8 DDR4, 42 PCIe lanes, 2 XBus 4B, 16 OpenCAPI lanes[20]

Sforza modules use a land grid array (LGA) 2601-pin socket.[21]

Systems

Raptor Computing Systems / Raptor Engineering

Talos II – two-socket workstation/server platform using POWER9 SMT4 Sforza processors;[22] available as 2U server, 4U server, tower, or EATX mainboard. Marketed as secure and owner-controllable with free and open-source software and firmware. Initially shipping with 4-core,[23] 8-core,[24] 18-core,[25] and 22-core[26] chip options until chips with more cores are available.[27][28]

Talos II Lite – single-socket version of the Talos II mainboard, made using the same PCB.[29]

Blackbird – single-socket microATX platform using SMT4 Sforza processors (up to 8-core 160 W variant), 4–8 cores, 2 RAM slots (supporting up to 256 GiB total)[30]

Google–Rackspace partnership

Barreleye G2 / Zaius – two-socket server platform using LaGrange processors;[22] both the Barreleye G2 and Zaius chassis use the Zaius POWER9 motherboard[31][32][33]

IBM

Power System AC922 – 2U, 2× POWER9 SMT4 Monza, with up to 6× Nvidia Volta GPUs, 2× CAPI 2.0 attached accelerators and 1 TiB DDR4 RAM. AC here is an abbreviation for Accelerated Computing; this system is also known as "Witherspoon" or "Newell".[22][34][35][36][37]

Power System L922 – 2U, 1–2× POWER9 SMT8, 8–12 cores per processor, up to 4 TiB DDR4 RAM (1 TiB = 1024 GiB), PowerVM running Linux.[38][39]

Power System S914 – 4U, 1× POWER9 SMT8, 4–8 cores, up to 1 TiB DDR4 RAM, PowerVM running AIX/IBM i/Linux.[38][39]

Power System S922 – 2U, 1–2× POWER9 SMT8, 4–11 cores per processor, up to 4 TiB DDR4 RAM, PowerVM running AIX/IBM i/Linux.[40]

Power System S924 – 4U, 2× POWER9 SMT8, 8–12 cores per processor, up to 4 TiB DDR4 RAM, PowerVM running AIX/IBM i/Linux.[38][39][41]

Power System H922 – 2U, 1–2× POWER9 SMT8, 4–10 cores per processor, up to 4 TiB DDR4 RAM, PowerVM running SAP HANA (on Linux) with AIX/IBM i on up to 25% of the system.[38][39][42]

Power System H924 – 4U, 2× POWER9 SMT8, 8–12 cores per processor, up to 4 TiB DDR4 RAM, PowerVM running SAP HANA (on Linux) with AIX/IBM i on up to 25% of the system.[38][39][42]

Power System E950 – 4U, 2–4× POWER9 SMT8, 8–12 cores per processor, up to 16 TiB buffered DDR4 RAM[43]

Power System E980 – 1–4× 4U, 4–16× POWER9 SMT8, 8–12 cores per processor, up to 64 TiB buffered DDR4 RAM[44]

Hardware Management Console 7063-CR2 – 1U, 1× POWER9 SMT8, 6 cores, 64-128 GB DDR4 RAM.[45]

Penguin Computing

Magna PE2112GTX – 2U, two-socket server for high performance computing using LaGrange processors. Manufactured by Wistron.[46]

IBM supercomputers

Summit and Sierra – The United States Department of Energy together with Oak Ridge National Laboratory and Lawrence Livermore National Laboratory contracted IBM and Nvidia to build two supercomputers, the Summit and the Sierra, are based on POWER9 processors coupled with Nvidia's Volta GPUs. These systems are slated to go online in 2017.[47][48][49] Sierra is based on IBM's Power Systems AC922 compute node.[35] The first racks of Summit were delivered to Oak Ridge National Laboratory on 31 July 2017.[50]

MareNostrum 4 – One of the three clusters in the emerging technologies block of the fourth MareNostrum supercomputer is a POWER9 cluster with Nvidia Volta GPUs. This cluster is expected to provide more than 1.5 petaflops of computing capacity when installed. The emerging technologies block of the MareNostrum 4 exists to test if new developments might be "suitable for future versions of MareNostrum".[51]

Operating system support

As with its predecessor, POWER9 is supported by FreeBSD,[52] IBM AIX, IBM i, Linux (both running with and without PowerVM), and OpenBSD.[53]

Implementation of POWER9 support in the Linux kernel began with version 4.6 in March 2016.[54]

Red Hat Enterprise Linux (RHEL), SUSE Linux Enterprise (SLES), Debian Linux, and CentOS are supported as of August 2018.[55][56][57][58]

The GNU Guix package manager also supports POWER9, but currently only with another operating system to host it, i.e. no GNU Guix System.[59]

See also

References

- Big Blue Aims For The Sky With Power9

- Shah, Agam (2016-08-23). "IBM's 24-core Power9 chip: 5 things you need to know". PCWorld.

- McCredie, Brad (April 2016). "OpenPOWER and the Roadmap Ahead" (presentation). OpenPOWER Foundation.

- Morgan, Timothy Prickett (2017-12-05). "Power9 To The People". The Next Platform.

the Nimbus Power9 chip used in the AC922 is a single chip module that has 24 cores on the die. The Summit and Sierra machines based on the AC922 are getting 22 core versions of the chips ... IBM could later, as Power9 yields improve, add a 24 core option.

- Williams, Chris (2016-04-07). "Power9: Google gives Intel a chip-flip migraine, IBM tries to lures big biz". The Register.

- "The 60th edition of the TOP500 List (November 2022)".

- "ORNL Launches Summit Supercomputer | ORNL".

- Add full Power ISA 3.0 / POWER9 binutils support

- The Prospects For A Power9 Revolution

- POWER9 XIVE interrupt controller

- IBM Power 9 XIVE Delivers IO Performance Improvement

- "Microwatt grows up" - Paul Mackerras (LCA 2021 Online)

- "The IBM POWER9 Scale Up Processor" (PDF).

AXON @25.6GHz vs DDR4 @ 3200 MHz

- "Raptor Computing Systems::CP9M01 Intro". www.raptorcs.com. Retrieved 2017-11-17.

- Nvidia's NVLink 2.0 will first appear in Power9 servers next year

- Stuecheli, Jeff (26 January 2017). "Webinar POWER9" (Video recording / slides). AIX Virtual User Group. - Slides (PDF) - AIX VUG page has links to slides and video

- Gangidi, Adi. "Let me comment on LaGrange POWER9". Twitter.

- IBM Portal for OpenPOWER - POWER9 - Sforza Module

- IBM Portal for OpenPOWER - POWER9 - Monza Module

- IBM Portal for OpenPOWER - POWER9 - LaGrange Module

- "T2P9D01 Mainboard User's Guide" (PDF). Raptor Computing Systems. 2018.

- Raptor Computing Systems Wiki - OpenPOWER

- "Raptor Computing Systems::CP9M01". www.raptorcs.com. Retrieved 2018-03-03.

- "Raptor Computing Systems::CP9M02". www.raptorcs.com. Retrieved 2018-03-03.

- "Raptor Computing Systems::CP9M06". www.raptorcs.com. Retrieved 2018-03-03.

- "Raptor Computing Systems::CP9M08". www.raptorcs.com. Retrieved 2018-05-20.

- "Raptor Computing Systems::TL2WK2" (product description). Raptor Computing Systems.

- "Raptor Computing Systems::Frequently Asked Questions". www.raptorcs.com. Retrieved 2017-11-17.

- "Talos II Lite Mainboard". Retrieved 2018-06-29.

- "Blackbird™ Mainboard (Board Only)". www.raptorcs.com. Retrieved 2019-02-01.

- Zipfel, John; Lippert, Rob. "Introducing Zaius, Google and Rackspace's open server running IBM POWER9" (blog post). Google Cloud Platform Blog. Google.

- Lippert, Rob; Sullivan, Aaron; Gangidi, Adi; Yeh, Poly (2016-12-07). "Zaius / Barreleye G2 Specification Chassis, Motherboard, Lunchbox Power Supply - Revision 0.5.3" (PDF). Github. Open Compute Project.

- Sullivan, Aaron (2017-03-08). "The Latest on Our Zaius /Barreleye G2 Open Compute-OpenPOWER Server" (blog post). The Official Rackspace Blog. Rackspace.

- David Bader - Twitter

- How you can Boost Acceleration with OpenCAPI, Today!

- IBM Power System AC922 (8335-GTG) server helps you to harness breakthrough accelerated AI, HPDA, and HPC performance for faster time to insight

- "IBM Power System AC922 - Details - United States". IBM Marketplace. 6 December 2017.

- https://www.theregister.co.uk/2018/02/14/ibm_power9_servers/ Big Blue levels up server sextet with POWER9 for IBM i, AIX, HANA, Linux

- https://www.nextplatform.com/2018/02/15/ins-outs-ibms-power9-zz-systems/ The Ins And Outs Of IBM’s Power9 ZZ Systems

- "IBM Power System S922 - Details". IBM.

- Griffiths, Nigel (14 February 2018). "IBM POWER9 Scale-Out S924 First Look" (video). YouTube.

- Morgan, Timothy Prickett (14 February 2018). "At Long Last, IBM i Finally Gets Power9 - IT Jungle". IT Jungle.

- "IBM Systems Hardware IBM Power System E950 Data Sheet" (PDF).

- "IBM Systems Hardware IBM Power System E980 Data Sheet" (PDF).

- IBM Power Systems delivers new Hardware Management Console for IBM POWER technology- based servers

- @TomJHill35 (2017-11-15). "@PenguinHPC showing off the results of true open collaboration with their latest #POWER9 system #openpower #hpc…" (Tweet). Retrieved 16 November 2017 – via Twitter.

- NVIDIA Volta, IBM POWER9 Land Contracts For New US Government Supercomputers

- ORNL Summit home page

- Lawrence Livermore signs contract with IBM

- ORNL building world’s smartest supercomputer

- "MareNostrum". BSC-CNS. Barcelona Supercomputing Center. Retrieved 30 October 2017.

- "FreeBSD revision introducing POWER9 CPU identifier to the system". svnweb.freebsd.org. Retrieved 2018-10-11.

- "First powerpc64 snapshots available". Retrieved 2020-07-07.

- "Linux 4.6 Begins Laying The Foundation For POWER9". Phoronix. March 18, 2016.

- "Red Hat Enterprise Linux 7.4 for IBM Power LE (POWER9) - Release Notes - Red Hat Customer Portal". access.redhat.com. Retrieved 2017-11-17.

- "PPC64 - Debian Wiki". wiki.debian.org. Retrieved 2017-11-17.

- "SUSE Linux Enterprise Server for POWER | SUSE". www.suse.com. Retrieved 2017-11-17.

- "Release for CentOS Linux 7 (1804) on POWER9 (ppc64le)". lists.centos.org. Retrieved 2018-08-15.

- "New Supported Platform: powerpc64le-linux". guix.gnu.org. Retrieved 2023-03-02.