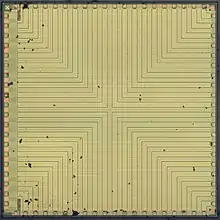

Power network design (IC)

In the design of integrated circuits, power network design is the analysis and design of on-chip conductor networks that distribute electrical power on a chip. As in all engineering, this involves tradeoffs - the network must have adequate performance, be sufficiently reliable, but should not use more resources than required.

Function

The power distribution network distributes power and ground voltages from pad locations to all devices in a design. Shrinking device dimensions, faster switching frequencies and increasing power consumption in deep sub-micrometer technologies cause large switching currents to flow in the power and ground networks which degrade performance and reliability. A robust power distribution network is essential to ensure reliable operation of circuits on a chip. Power supply integrity verification is a critical concern in high-performance designs.

Design considerations

Due to the resistance of the interconnects constituting the network, there is a voltage drop across the network, commonly referred to as the IR-drop. The package supplies currents to the pads of the power grid either by means of package leads in wire-bond chips or through C4 bump arrays in flip chip technology. Although the resistance of package is quite small, the inductance of package leads is significant which causes a voltage drop at the pad locations due to the time varying current drawn by the devices on die. This voltage drop is referred to as the di/dt-drop. Therefore, the voltage seen at the devices is the supply voltage minus the IR-drop and di/dt-drop.

Excessive voltage drops in the power grid reduce switching speeds and noise margins of circuits, and inject noise which might lead to functional failures. High average current densities lead to undesirable wearing out of metal wires due to electromigration (EM). Therefore, the challenge in the design of a power distribution network is in achieving excellent voltage regulation at the consumption points notwithstanding the wide fluctuations in power demand across the chip, and to build such a network using minimum area of the metal layers. These issues are prominent in high performance chips such as microprocessors, since large amounts of power have to be distributed through a hierarchy of many metal layers. A robust power distribution network is vital in meeting performance guarantees and ensuring reliable operation.

Capacitance between power and ground distribution networks, referred to as decoupling capacitors or decaps, acts as local charge storage and is helpful in mitigating the voltage drop at supply points. Parasitic capacitance between metal wires of supply lines, device capacitance of the non-switching devices, and capacitance between N-well and substrate, occur as implicit decoupling capacitance in a power distribution network. Unfortunately, this implicit decoupling capacitance is sometimes not enough to constrain the voltage drop within safe bounds and designers often have to add intentional explicit decoupling capacitance structures on the die at strategic locations. These explicitly added decoupling capacitances are not free and increase the area and leakage power consumption of the chip. Parasitic interconnect resistance, decoupling capacitance and package/interconnect inductance form a complex RLC circuit which has its own resonance frequency. If the resonance frequency lies close to the operating frequency of the design, large voltage drops can develop in the grid.

The crux of the problem in designing a power grid is that there are many unknowns until the very end of the design cycle. Nevertheless, decisions about the structure, size and layout of the power grid have to be made at very early stages when a large part of the chip design has not even begun. Unfortunately, most commercial tools focus on post-layout verification of the power grid when the entire chip design is complete and detailed information about the parasitics of the power and ground lines and the currents drawn by the transistors are known. Power grid problems revealed at this stage are usually very difficult or expensive to fix, so the preferred methodologies help to design an initial power grid and refine it progressively at various design stages.

Due to the growth in power consumption and switching speeds of modern high performance microprocessors, the di/dt effects are becoming a growing concern in high speed designs. Clock gating, which is a preferred scheme for power management of high performance designs, can cause rapid surges in current demands of macro-blocks and increase di/dt effects. Designers rely on the on-chip parasitic capacitances and intentionally added decoupling capacitors to counteract the di/dt variations in the voltage. But it is necessary to model accurately the inductance and capacitance of the package and chip and analyze the grid with such models, as otherwise the amount of decoupling to be added might be underestimated or overestimated. Also it is necessary to maintain the efficiency of the analysis even when including these detailed models.

Analysis

A critical issue in the analysis of power grids is the large size of the network (typically millions of nodes in a state-of-the-art microprocessor). Simulating all the non-linear devices in the chip together with the power grid is computationally infeasible. To make the size manageable, the simulation is done in two steps. First, the non-linear devices are simulated assuming perfect supply voltages and the currents drawn by the devices are measured. Next, these devices are modeled as independent time-varying current sources for simulating the power grid and the voltage drops at the transistors are measured. Since voltage drops are typically less than 10% of the power supply voltage, the error incurred by ignoring the interaction between the device currents and the supply voltage is small. By doing these two steps, the power grid analysis problem reduces to solving a linear network which is still quite large. To further reduce the network size, we can exploit the hierarchy in the power distribution models.

The circuit currents are not independent due to signal correlations between blocks. This is addressed by deriving the inputs for individual blocks of the chip from the results of logic simulation using a common set of chip-wide input patterns. An important issue in power grid analysis is to determine what these input patterns should be. For IR-drop analysis, patterns that produce maximum instantaneous currents are required, whereas for electromigration purposes, patterns producing large sustained (average) currents are of interest.

Power grid analysis can be classified into input vector dependent[1][2] methods and vectorless[3] methods. The input vector pattern dependent methods employ search techniques to find a set of input patterns which cause the worst drop in the grid. A number of methods have been proposed in literature which use genetic algorithms or other search techniques to find vectors or a pattern of vectors that maximize the total current drawn from the supply network. Input vector-pattern dependent approaches are computationally intensive and are limited to circuit blocks rather than full-chip analysis. Furthermore, these approaches are inherently optimistic, underestimating the voltage drop and thus letting some of the supply noise problems go unnoticed. The vectorless approaches, on the other hand, aim to compute an upper bound on the worst-case drop in an efficient manner. These approaches have the advantage of being fast and conservative, but are sometimes too conservative, leading to overdesign.[4]

Most of the literature on power network analysis deals with the issue of computing the worst voltage drops in the power network. Electromigration is an equally serious concern, but is attacked with almost identical methods. Instead of the voltage at each node, EM analysis solves for current in each branch, and instead of a voltage limit, there is a current limit per wire, depending on its layer and width.

Other IC applications may use only a portions of the flows mentioned here. A gate array or field programmable gate array (FPGA) designer, for example, will only do the design stages, since the detailed usage of these parts is not known when the power supply must be designed. Likewise, a user of FPGAs or gate arrays will only use the analysis portion, as the design is already fixed.

See also

References

- Electronic Design Automation For Integrated Circuits Handbook, by Lavagno, Martin, and Scheffer, ISBN 0-8493-3096-3 A survey of the field of electronic design automation. This summary was derived (with permission) from Vol II, Chapter 20, Design and Analysis of Power Supply Networks, by David Blaauw, Sanjay Pant, Rajat Chaudhry, and Rajendran Panda.