Fin field-effect transistor

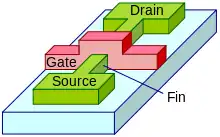

A fin field-effect transistor (FinFET) is a multigate device, a MOSFET (metal–oxide–semiconductor field-effect transistor) built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double or even multi gate structure. These devices have been given the generic name "FinFETs" because the source/drain region forms fins on the silicon surface. The FinFET devices have significantly faster switching times and higher current density than planar CMOS (complementary metal–oxide–semiconductor) technology.[1]

FinFET is a type of non-planar transistor, or "3D" transistor.[2] It is the basis for modern nanoelectronic semiconductor device fabrication. Microchips utilizing FinFET gates first became commercialized in the first half of the 2010s, and became the dominant gate design at 14 nm, 10 nm and 7 nm process nodes.

It is common for a single FinFET transistor to contain several fins, arranged side by side and all covered by the same gate, that act electrically as one, to increase drive strength and performance.[3]

History

After the MOSFET was first demonstrated by Mohamed Atalla and Dawon Kahng of Bell Labs in 1960,[4] the concept of a double-gate thin-film transistor (TFT) was proposed by H. R. Farrah (Bendix Corporation) and R. F. Steinberg in 1967.[5] A double-gate MOSFET was later proposed by Toshihiro Sekigawa of the Electrotechnical Laboratory (ETL) in a 1980 patent describing the planar XMOS transistor.[6] Sekigawa fabricated the XMOS transistor with Yutaka Hayashi at the ETL in 1984. They demonstrated that short-channel effects can be significantly reduced by sandwiching a fully depleted silicon-on-insulator (SOI) device between two gate electrodes connected together.[7][8]

The first FinFET transistor type was called a "Depleted Lean-channel Transistor" or "DELTA" transistor, which was first fabricated in Japan by Hitachi Central Research Laboratory's Digh Hisamoto, Toru Kaga, Yoshifumi Kawamoto and Eiji Takeda in 1989.[7][9][10] The gate of the transistor can cover and electrically contact the semiconductor channel fin on both the top and the sides or only on the sides. The former is called a tri-gate transistor and the latter a double-gate transistor. A double-gate transistor optionally can have each side connected to two different terminal or contacts. This variant is called split transistor. This enables more refined control of the operation of the transistor.

Indonesian engineer Effendi Leobandung, while working at the University of Minnesota, published a paper with Stephen Y. Chou at the 54th Device Research Conference in 1996 outlining the benefit of cutting a wide CMOS transistor into many channels with narrow width to improve device scaling and increase device current by increasing the effective device width.[11] This structure is what a modern FinFET looks like. Although some device width is sacrificed by cutting it into narrow widths, the conduction of the side wall of narrow fins more than make up for the loss, for tall fins.[12] The device had a 35 nm channel width and 70 nm channel length.[11]

The potential of Digh Hisamoto's research on DELTA transistors drew the attention of the Defense Advanced Research Projects Agency (DARPA), which in 1997 awarded a contract to a research group at the University of California, Berkeley to develop a deep sub-micron transistor based on DELTA technology.[13] The group was led by Hisamoto along with TSMC's Chenming Hu. The team made the following breakthroughs between 1998 and 2004.[14]

- 1998 – N-channel FinFET (17 nm) – Digh Hisamoto, Chenming Hu, Tsu-Jae King Liu, Jeffrey Bokor, Wen-Chin Lee, Jakub Kedzierski, Erik Anderson, Hideki Takeuchi, Kazuya Asano[15]

- 1999 – P-channel FinFET (sub-50 nm) – Digh Hisamoto, Chenming Hu, Xuejue Huang, Wen-Chin Lee, Charles Kuo, Leland Chang, Jakub Kedzierski, Erik Anderson, Hideki Takeuchi[16]

- 2001 – 15 nm FinFET – Chenming Hu, Yang-Kyu Choi, Nick Lindert, P. Xuan, S. Tang, D. Ha, Erik Anderson, Tsu-Jae King Liu, Jeffrey Bokor[17]

- 2002 – 10 nm FinFET – Shibly Ahmed, Scott Bell, Cyrus Tabery, Jeffrey Bokor, David Kyser, Chenming Hu, Tsu-Jae King Liu, Bin Yu, Leland Chang[18]

- 2004 – High-κ/metal gate FinFET – D. Ha, Hideki Takeuchi, Yang-Kyu Choi, Tsu-Jae King Liu, W. Bai, D.-L. Kwong, A. Agarwal, M. Ameen

They coined the term "FinFET" (fin field-effect transistor) in a December 2000 paper,[19] used to describe a non-planar, double-gate transistor built on an SOI substrate.[20]

In 2006, a team of Korean researchers from the Korea Advanced Institute of Science and Technology (KAIST) and the National Nano Fab Center developed a 3 nm transistor, the world's smallest nanoelectronic device, based on gate-all-around (GAA) FinFET technology.[21][22] In 2011, Rice University researchers Masoud Rostami and Kartik Mohanram demonstrated that FinFETs can have two electrically independent gates, which gives circuit designers more flexibility to design with efficient, low-power gates.[23]

In 2020, Chenming Hu received the IEEE Medal of Honor award for his development of the FinFET, which the Institute of Electrical and Electronics Engineers (IEEE) credited with taking transistors to the third dimension and extending Moore's law.[24]

Commercialization

The industry's first 25 nanometer transistor operating on just 0.7 volts was demonstrated in December 2002 by TSMC. The "Omega FinFET" design, named after the similarity between the Greek letter "Omega" and the shape in which the gate wraps around the source/drain structure, has a gate delay of just 0.39 picosecond (ps) for the N-type transistor and 0.88 ps for the P-type.

In 2004, Samsung demonstrated a "Bulk FinFET" design, which made it possible to mass-produce FinFET devices. They demonstrated dynamic random-access memory (DRAM) manufactured with a 90 nm Bulk FinFET process.[14]

In 2011, Intel demonstrated tri-gate transistors, where the gate surrounds the channel on three sides, allowing for increased energy efficiency and lower gate delay—and thus greater performance—over planar transistors.[25][26][27]

Commercially produced chips at 22 nm and below have generally utilised FinFET gate designs (but planar processes do exist down to 18 nm, with 12 nm in development). Intel's tri-gate variant were announced at 22 nm in 2011 for its Ivy Bridge microarchitecture.[28] These devices shipped from 2012 onwards. From 2014 onwards, at 14 nm (or 16 nm) major foundries (TSMC, Samsung, GlobalFoundries) utilised FinFET designs.

In 2013, SK Hynix began commercial mass-production of a 16 nm process,[29] TSMC began production of a 16 nm FinFET process,[30] and Samsung Electronics began production of a 10 nm process.[31] TSMC began production of a 7 nm process in 2017,[32] and Samsung began production of a 5 nm process in 2018.[33] In 2019, Samsung announced plans for the commercial production of a 3 nm GAAFET process by 2021.[34]

Commercial production of nanoelectronic FinFET semiconductor memory began in the 2010s.[1] In 2013, SK Hynix began mass-production of 16 nm NAND flash memory,[29] and Samsung Electronics began production of 10 nm multi-level cell (MLC) NAND flash memory.[31] In 2017, TSMC began production of SRAM memory using a 7 nm process.[32]

See also

References

- Kamal, Kamal Y. (2022). "The Silicon Age: Trends in Semiconductor Devices Industry" (PDF). Journal of Engineering Science and Technology Review. 15 (1): 110–115. doi:10.25103/jestr.151.14. ISSN 1791-2377. S2CID 249074588. Retrieved 2022-05-26.

- "What is Finfet?". Computer Hope. April 26, 2017. Retrieved 4 July 2019.

- Shimpi, Anand Lal (4 May 2011). "Intel Announces first 22nm 3D Tri-Gate Transistors, Shipping in 2H 2011". AnandTech. Retrieved 18 January 2022.

- "1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine. Computer History Museum. Retrieved 25 September 2019.

- Farrah, H. R.; Steinberg, R. F. (February 1967). "Analysis of double-gate thin-film transistor". IEEE Transactions on Electron Devices. 14 (2): 69–74. Bibcode:1967ITED...14...69F. doi:10.1109/T-ED.1967.15901.

- Koike, Hanpei; Nakagawa, Tadashi; Sekigawa, Toshiro; Suzuki, E.; Tsutsumi, Toshiyuki (23 February 2003). "Primary Consideration on Compact Modeling of DG MOSFETs with Four-terminal Operation Mode". TechConnect Briefs. 2 (2003): 330–333. S2CID 189033174.

- Colinge, J. P. (2008). FinFETs and Other Multi-Gate Transistors. Springer Science & Business Media. pp. 11 & 39. ISBN 9780387717517.

- Sekigawa, Toshihiro; Hayashi, Yutaka (August 1984). "Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate". Solid-State Electronics. 27 (8): 827–828. Bibcode:1984SSEle..27..827S. doi:10.1016/0038-1101(84)90036-4. ISSN 0038-1101.

- Hisamoto, Digh; Kaga, Toru; Kawamoto, Yoshifumi; Takeda, Eiji (December 1989). "A fully depleted lean-channel transistor (DELTA)—a novel vertical ultra thin SOI MOSFET". International Technical Digest on Electron Devices Meeting: 833–836. doi:10.1109/IEDM.1989.74182. S2CID 114072236.

- "IEEE Andrew S. Grove Award Recipients". IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Retrieved 4 July 2019.

- Leobandung, Effendi; Chou, Stephen Y. (1996). "Reduction of short channel effects in SOI MOSFETs with 35 nm channel width and 70 nm channel length". 1996 54th Annual Device Research Conference Digest. pp. 110–111. doi:10.1109/DRC.1996.546334. ISBN 0-7803-3358-6. S2CID 30066882.

- Leobandung, Effendi (June 1996). Nanoscale MOSFETs and single charge transistors on SOI (Ph.D. thesis). Minneapolis, Minnesota: University of Minnesota. p. 72.

- "The Breakthrough Advantage for FPGAs with Tri-Gate Technology" (PDF). Intel. 2014. Retrieved 4 July 2019.

- Tsu-Jae King, Liu (June 11, 2012). "FinFET: History, Fundamentals and Future". University of California, Berkeley. Symposium on VLSI Technology Short Course. Archived from the original on 28 May 2016. Retrieved 9 July 2019.

- Hisamoto, Digh; Hu, Chenming; Liu, Tsu-Jae King; Bokor, Jeffrey; Lee, Wen-Chin; Kedzierski, Jakub; Anderson, Erik; Takeuchi, Hideki; Asano, Kazuya (December 1998). "A folded-channel MOSFET for deep-sub-tenth micron era". International Electron Devices Meeting 1998. Technical Digest (Cat. No.98CH36217). pp. 1032–1034. doi:10.1109/IEDM.1998.746531. ISBN 0-7803-4774-9. S2CID 37774589.

- Hisamoto, Digh; Kedzierski, Jakub; Anderson, Erik; Takeuchi, Hideki (December 1999). "Sub 50-nm FinFET: PMOS" (PDF). International Electron Devices Meeting 1999. Technical Digest (Cat. No.99CH36318). pp. 67–70. doi:10.1109/IEDM.1999.823848. ISBN 0-7803-5410-9. S2CID 7310589.

- Hu, Chenming; Choi, Yang-Kyu; Lindert, N.; Xuan, P.; Tang, S.; Ha, D.; Anderson, E.; Bokor, J.; Tsu-Jae King, Liu (December 2001). "Sub-20 nm CMOS FinFET technologies". International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224). pp. 19.1.1–19.1.4. doi:10.1109/IEDM.2001.979526. ISBN 0-7803-7050-3. S2CID 8908553.

- Ahmed, Shibly; Bell, Scott; Tabery, Cyrus; Bokor, Jeffrey; Kyser, David; Hu, Chenming; Liu, Tsu-Jae King; Yu, Bin; Chang, Leland (December 2002). "FinFET scaling to 10 nm gate length" (PDF). Digest. International Electron Devices Meeting. pp. 251–254. CiteSeerX 10.1.1.136.3757. doi:10.1109/IEDM.2002.1175825. ISBN 0-7803-7462-2. S2CID 7106946.

- Hisamoto, Digh; Hu, Chenming; Bokor, J.; King, Tsu-Jae; Anderson, E.; et al. (December 2000). "FinFET—a self-aligned double-gate MOSFET scalable to 20 nm". IEEE Transactions on Electron Devices. 47 (12): 2320–2325. Bibcode:2000ITED...47.2320H. CiteSeerX 10.1.1.211.204. doi:10.1109/16.887014.

- Hisamoto, Digh; Hu, Chenming; Huang, Xuejue; Lee, Wen-Chin; Kuo, Charles; et al. (May 2001). "Sub-50 nm P-channel FinFET" (PDF). IEEE Transactions on Electron Devices. 48 (5): 880–886. Bibcode:2001ITED...48..880H. doi:10.1109/16.918235.

- "Still Room at the Bottom.(nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology )", Nanoparticle News, 1 April 2006, archived from the original on 6 November 2012, retrieved 6 July 2019

- Lee, Hyunjin; et al. (2006). "Sub-5nm All-Around Gate FinFET for Ultimate Scaling". 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers. pp. 58–59. doi:10.1109/VLSIT.2006.1705215. hdl:10203/698. ISBN 978-1-4244-0005-8. S2CID 26482358.

- Rostami, M.; Mohanram, K. (2011). "Dual-Vth Independent-Gate FinFETs for Low Power Logic Circuits" (PDF). IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 30 (3): 337–349. doi:10.1109/TCAD.2010.2097310. hdl:1911/72088. S2CID 2225579.

- "How the Father of FinFETs Helped Save Moore's Law: Chenming Hu, the 2020 IEEE Medal of Honor recipient, took transistors into the third dimension". IEEE Spectrum. 21 April 2020. Retrieved 27 December 2021.

- Bohr, Mark; Mistry, Kaizad (May 2011). "Intel's Revolutionary 22 nm Transistor Technology" (PDF). intel.com. Retrieved April 18, 2018.

- Grabham, Dan (May 6, 2011). "Intel's Tri-Gate transistors: everything you need to know". TechRadar. Retrieved April 19, 2018.

-

Bohr, Mark T.; Young, Ian A. (2017). "CMOS Scaling Trends and Beyond". IEEE Micro. 37 (6): 20–29. doi:10.1109/MM.2017.4241347. S2CID 6700881.

The next major transistor innovation was the introduction of FinFET (tri-gate) transistors on Intel's 22-nm technology in 2011.

- "Intel 22nm 3-D Tri-Gate Transistor Technology". Intel Newsroom.

- "History: 2010s". SK Hynix. Retrieved 8 July 2019.

- "16/12nm Technology". TSMC. Retrieved 30 June 2019.

- "Samsung Mass Producing 128Gb 3-bit MLC NAND Flash". Tom's Hardware. 11 April 2013. Retrieved 21 June 2019.

- "7nm Technology". TSMC. Retrieved 30 June 2019.

- Shilov, Anton. "Samsung Completes Development of 5nm EUV Process Technology". www.anandtech.com. Retrieved 2019-05-31.

- Armasu, Lucian (11 January 2019), "Samsung Plans Mass Production of 3nm GAAFET Chips in 2021", www.tomshardware.com