Xilinx ISE

Xilinx ISE[2] (Integrated Synthesis Environment)[3] is a discontinued software tool from Xilinx for synthesis and analysis of HDL designs, which primarily targets development of embedded firmware for Xilinx FPGA and CPLD integrated circuit (IC) product families. It was succeeded by Xilinx Vivado. Use of the last released edition from October 2013 continues for in-system programming of legacy hardware designs containing older FPGAs and CPLDs otherwise orphaned by the replacement design tool, Vivado Design Suite.

| |

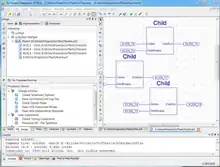

Xilinx ISE WebPack 14.4 running on Windows 8 | |

| Developer(s) | Xilinx |

|---|---|

| Final release | |

| Operating system | RHEL, SLED, FreeBSD, Microsoft Windows |

| Size | 23.43 Gigabytes |

| Available in | English |

| Type | EDA |

| License | Shareware |

| Website | xilinx |

ISE enables the developer to synthesize ("compile") their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer. Other components shipped with the Xilinx ISE include the Embedded Development Kit (EDK), a Software Development Kit (SDK) and ChipScope Pro.[4] The Xilinx ISE is primarily used for circuit synthesis and design, while ISIM or the ModelSim logic simulator is used for system-level testing.[5][6]

As commonly practiced in the commercial electronic design automation sector, Xilinx ISE is tightly-coupled to the architecture of Xilinx's own chips (the internals of which are highly proprietary) and cannot be used with FPGA products from other vendors.[3] Given the highly proprietary nature of the Xilinx hardware product lines, it is rarely possible to use open source alternatives to tooling provided directly from Xilinx, although as of 2020, some exploratory attempts are being made.[7]

Legacy status

Since 2012, Xilinx ISE has been discontinued in favor of Vivado Design Suite that serves the same roles as ISE with additional features for system on a chip development.[8][9] Xilinx released the last version of ISE in October 2013 (version 14.7), and states that "ISE has moved into the sustaining phase of its product life cycle, and there are no more planned ISE releases."[1]

User Interface

The primary user interface of the ISE is the Project Navigator, which includes the design hierarchy (Sources), a source code editor (Workplace), an output console (Transcript), and a processes tree (Processes).[3][10]

The Design hierarchy consists of design files (modules), whose dependencies are interpreted by the ISE and displayed as a tree structure.[3] For single-chip designs there may be one main module, with other modules included by the main module, similar to the main() subroutine in C++ programs.[3] Design constraints are specified in modules, which include pin configuration and mapping.[3]

The Processes hierarchy describes the operations that the ISE will perform on the currently active module.[3] The hierarchy includes compilation functions, their dependency functions, and other utilities.[3] The window also denotes issues or errors that arise with each function.[3]

The Transcript window provides status of currently running operations, and informs engineers on design issues.[3] Such issues may be filtered to show Warnings, Errors, or both.[3]

Simulation

System-level testing may be performed with ISIM or the ModelSim logic simulator, and such test programs must also be written in HDL languages.[3] Test bench programs may include simulated input signal waveforms, or monitors which observe and verify the outputs of the device under test.[3]

ModelSim or ISIM may be used to perform the following types of simulations:[5]

- Logical verification, to ensure the module produces expected results

- Behavioural verification, to verify logical and timing issues

- Post-place & route simulation, to verify behaviour after placement of the module within the reconfigurable logic of the FPGA

Synthesis

Xilinx's patented algorithms for synthesis allow designs to run up to 30% faster than competing programs, and allows greater logic density which reduces project time and costs.[11]

Also, due to the increasing complexity of FPGA fabric, including memory blocks and I/O blocks, more complex synthesis algorithms were developed that separate unrelated modules into slices, reducing post-placement errors.[11]

IP Cores are offered by Xilinx and other third-party vendors, to implement system-level functions such as digital signal processing (DSP), bus interfaces, networking protocols, image processing, embedded processors, and peripherals.[11] Xilinx has been instrumental in shifting designs from ASIC-based implementation to FPGA-based implementation.[11]

Editions

The Subscription Edition is the licensed version of Xilinx ISE, and a free trial version is available for download.

The Web Edition is the free version of Xilinx ISE, that can be downloaded and used for no charge. It provides synthesis and programming for a limited number of Xilinx devices. In particular, devices with a large number of I/O pins and large gate matrices are disabled.

The low-cost Spartan family of FPGAs is fully supported by this edition, as well as the family of CPLDs, meaning small developers and educational institutions have no overheads from the cost of development software.

License registration is required to use the Web Edition of Xilinx ISE, which is free and can be renewed an unlimited number of times.

Device Support

Hardware Support

ISE supports up to Spartan 6, and the older devices including CPLDs (XC9500 and CoolRunner).[12] For development targeting newer Xilinx's devices (7 series, UltraScale and UltraScale+ series), the Xilinx Vivado has to be used.

Operating System Support

Xilinx officially supports Microsoft Windows Version 7 64 bit, Red Hat Enterprise 4, 5, & 6 Workstations (32 & 64 bits) and SUSE Linux Enterprise 11 (32 & 64 bits).[13] Certain other Linux distributions can run Xilinx ISE WebPack with some modifications or configurations, including Gentoo Linux, Arch Linux, FreeBSD and Fedora.[14][15][16][17]

See also

References

- ISE 14.7 Updates, Xilinx Downloads

- "Foundation Series ISE 3.1i User Guide" (PDF). 100728 xilinx.com

- Handbook of Networked and Embedded Control Systems, Springer Science & Business Media, 14-Nov-2007

- Embedded Systems Design with Platform FPGAs, Morgan Kaufmann, 10-Sep-2010

- Circuit Design with VHDL, MIT Press, 2004

- Advances in Computer Science and Information Engineering, Springer Science & Business Media, 11-May-2012

- Shirriff, Ken (September 2020). "Reverse-engineering the first FPGA chip, the XC2064". righto.com. self-published blog of hardcore reversing-engineering specialist. Retrieved 25 September 2020.

I've determined how most of the XC2064 bitstream is configured ... and I've made a program to generate the CLB information from a bitstream file ... unfortunately, this is one of those projects where the last 20% takes most of the time, so there's still work to be done.

- "Xilinx Inc, Form 10-K, Annual Report, Filing Date May 25, 2012". secdatabase.com. Retrieved May 6, 2018.

- Vivado Design Suite, First version released in 2012, Xilinx Downloads

- FPGA Prototyping By Verilog Examples, John Wiley & Sons, 20-Sep-2011

- The Digital Consumer Technology Handbook, Elsevier, 30-Apr-2004

- "ISE Design Suite Product Table" (PDF). Retrieved 2020-08-09.

- "Chapter 3: Architecture Support and Requirements". ISE Design Suite 13: Release Notes Guide (PDF). Xilinx, Inc. 2012-01-25. p. 50.

- "Xilinx ISE Webpack 11". Gentoo Wiki. Gentoo Community. Archived from the original on October 7, 2012. Retrieved 8 May 2012.

- "Xilinx ISE WebPACK". Arch Wiki. Arch Community. Retrieved 8 May 2012.

- "Installed Xilinx ISE WebPack 12.1 on Fedora 12 x86_64". What's All This Brouhaha?. Wordpress. Archived from the original on March 3, 2011. Retrieved 8 May 2012.

- Koszek, Wojciech. "Working with Xilinx FPGAs on FreeBSD". FreeBSD. Retrieved 8 May 2012.