UNI/O

The UNI/O bus /ˌjuːniˈoʊ/ is an asynchronous serial bus created by Microchip Technology for low speed communication in embedded systems.[1] The bus uses a master/slave configuration, requiring one signal to pass data between devices. The first devices supporting the UNI/O bus were released in May 2008.

Interface

The UNI/O bus requires one logic signal:

- SCIO — Serial Clock, Data Input/Output[2]

Only one master device is allowed per bus, but multiple slave devices can be connected to a single UNI/O bus. Individual slaves are selected through an 8-bit to 12-bit address included in the command overhead.

Both master and slave devices use a tri-stateable, push-pull I/O pin to connect to SCIO, with the pin being placed in a high impedance state when not driving the bus. Because push-pull outputs are used, the output driver on slave devices is current-limited to prevent high system currents from occurring during bus collisions.

The idle state of the UNI/O bus is logic high. A pull-up resistor can be used to ensure the bus remains idle when no device is driving SCIO, but is not required for operation.[3]

Data encoding

Bit encoding

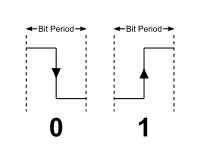

Clock and data signals are combined and communicated on the bus through Manchester encoding. This means that each data bit is transmitted in a fixed amount of time (called the "bit period").

The UNI/O specification places certain rules on the bit period:

- It is determined by the master.

- Slaves are required to synchronize with the master to recover the bit period during the start header.

- It can be within 10 µs and 100 µs (corresponding to a bit rate of 100 kbit/s to 10 kbit/s, respectively).

- It is only required to be fixed within a single bus operation (for new bus operations, the master can choose a different bit period).

In accordance with Manchester encoding, the bit value is defined by a signal transition in the middle of the bit period. UNI/O uses the IEEE 802.3 convention for defining 0 and 1 values:

- A high-to-low transition signifies a 0.

- A low-to-high transition signifies a 1.

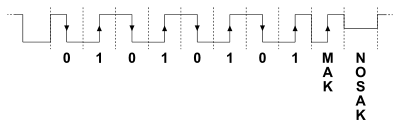

Bit periods occur back-to-back, with no delay between bit periods allowed.

Data words

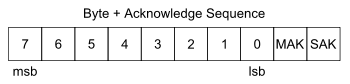

UNI/O uses 8-bit data words for communication. Bytes are transmitted msb first.

Acknowledge sequence

To facilitate error detection, a 2-bit wide "acknowledge sequence" is appended to the end of every data byte transmitted. The first bit is called the "master acknowledge" (shortened to "MAK") and is always generated by the master. The second bit, called the "slave acknowledge" (shortened to "SAK"), is always generated by the slave.

The MAK bit is used in the following manner:

- The master transmits a 1 bit (a MAK) to indicate to the slave that the bus operation will be continued.

- The master transmits a 0 bit (a NoMAK) to indicate that the preceding byte was the last byte for that bus operation.

The SAK bit is used in the following manner:

- Once a full device address has been transmitted (and a valid slave has been selected), if the previous data byte and subsequent MAK bit were received correctly, the slave transmits a 1 bit (a SAK).

- If an error occurs, the slave automatically shuts down and ignores further communication until a standby pulse is received. In this scenario, nothing will be transmitted during the SAK bit period. This missing transition can be detected by the master and is considered a NoSAK bit.

Command structure

Standby pulse

UNI/O defines a signal pulse, called the "standby pulse", that can be generated by the master to force slave devices into a reset state (referred to as "standby mode"). To generate a standby pulse, the master must drive the bus to a logic high for a minimum of 600 µs.

A standby pulse is required to be generated under certain conditions:

- Before initiating a command when selecting a new device (including after a POR/BOR event)

- After an error is detected

If a command is completed without error, a new command to the same device can be initiated without generating a standby pulse.

Start header

The start header is a special byte sequence defined by the UNI/O specification, and is used to initiate a new command. The start header consists of the following elements:

- The master drives the bus low for a minimum of 5 µs.

- The master outputs a 0x55 data byte.

- Slave devices measure the time necessary to receive the 0x55 byte by counting signal transitions. This time is then used by the slaves to determine the bit period and synchronize with the master.

- The master outputs a 1 for the MAK bit.

- The slave devices do not respond during the SAK bit following the start header. This is to avoid bus collisions which would occur of all slave devices tried to respond at the same time.

Device address

After the start header has been transmitted, the master must transmit a device address to select the desired slave device for the current operation. Once the device address has been sent, any slave device with an address different from that specified is required to shut down and ignore all further communication until a standby pulse is received.

UNI/O allows for both 8-bit and 12-bit device addresses. 8-bit addressing offers better data throughput due to less command overhead, while 12-bit addressing allows for more slaves with a common family code to exist on a single bus. When a slave device is designed, the designer must choose which addressing scheme to use.

8-bit addressing

For 8-bit addressing, the entire device address is transmitted in a single byte. The most significant 4 bits indicate the "family code", which is defined by Microchip in the UNI/O bus specification. The least significant 4 bits indicate the device code. The device code allows multiple slave devices with a common family code to be used on the same bus. The device code can be fixed for a given slave or customizable by the user. Choosing a device code and how it can be customized (if necessary) are the responsibilities of the slave device designer.

The current family codes for 8-bit devices, as of November 22, 2009,[1] are as follows:

| Family Code | Description |

|---|---|

| ′0000′ | Reserved |

| ′0011′ | Display Controllers |

| ′0100′ | I/O port expanders |

| ′1000′ | Frequency/Quadrature/PWM encoders, real-time clocks |

| ′1001′ | Temperature sensors |

| ′1010′ | EEPROMs |

| ′1011′ | Encryption/Authentication Devices |

| ′1100′ | DC/DC Converters |

| ′1101′ | A/D converters |

| ′1111′ | 12-bit addressable devices |

12-bit addressing

For 12-bit addressing, the device address is sent in two bytes. The most significant 4 bits of the first byte (which would correspond to the family code in 8-bit addressing), are set to ′1111′. The next 4 bits are the family code for the 12-bit address, and the second byte of the address is an 8-bit wide device code. The device code follows the same guidelines for definition as with 8-bit addressing.

Because the specified slave device is not selected until both bytes of the device address have been received, a NoSAK will occur during the acknowledge sequence following the first device address byte.

The current family codes for 12-bit devices, as of November 22, 2009,[1] are as follows:

| Family Code | Description |

|---|---|

| ′0000′ | Reserved |

| ′1111′ | Reserved |

Command byte

After the master has transmitted the device address and selected an individual slave, the master must transmit the 8-bit value for the specific command to be executed by the slave. The available commands are determined by the designer of each slave device, and will vary from slave to slave, e.g. a serial EEPROM will likely have different commands than a temperature sensor. The slave device designer will also determine if and how many data bytes are necessary for the execution of a command. If any data bytes are necessary, they are transmitted by either the master or the slave (dictated by the command type) after the command byte.

Communication will continue until either the master transmits a 0 (NoMAK) during the acknowledge sequence, or an error occurs. Assuming no errors occur, this means that commands can continue indefinitely if the master chooses.

Bus Parasitic Power

Some UNI/O Parts can be powered from the bus, eliminating the need for a dedicated supply voltage/wire.[4][5][6]

References

- UNI/O Bus Specification (PDF), retrieved 2009-11-22

- 1K-16K UNI/O Serial EEPROM Family Data Sheet (PDF), retrieved 2009-10-21

- AN1194, Recommended Usage of Microchip UNI/O Bus-Compatible Serial EEPROMs (PDF), retrieved 2009-10-21

- https://www.microchip.com/en-us/products/memory/serial-eeprom/single-wire-and-uniobus-serial-eeproms

- https://ww1.microchip.com/downloads/en/Appnotes/01213B.pdf

- https://ww1.microchip.com/downloads/en/DeviceDoc/22199b.pdf

External links

- UNI/O Bus Specification - Microchip