TO-3

In electronics, TO-3 is a designation for a standardized metal semiconductor package used for power semiconductors, including transistors, silicon controlled rectifiers, and, integrated circuits. TO stands for "Transistor Outline" and relates to a series of technical drawings produced by JEDEC.[1]

.jpg.webp)

The TO-3 case has a flat surface which can be attached to a heatsink, normally via a thermally conductive but electrically insulating washer. The design originated at Motorola around 1955 from a group headed by Dr. Virgil E. Bottom.[2] who was director of research of the Motorola Semiconductor Division. The first use of this design was for the germanium alloy-junction power transistor 2N176 – the first power transistor to be put into quantity production.[2][3] The lead spacing was originally intended to allow plugging the device into a then-common tube socket.[4]

Typical applications

The metal package can be attached to a heat sink, making it suitable for devices dissipating several watts of heat. Thermal compound is used to improve heat transfer between the device case and the heat sink. Since the device case is one of the electrical connections, an insulator may be required to electrically isolate the component from the heatsink. Insulating washers may be made of mica or other materials with good thermal conductivity.

The case is used with high-power and high-current devices, on the order of a few tens of amperes current and up to a hundred watts of heat dissipation. The case surfaces are metal for good heat conductivity and durability. The metal-to-metal and metal-to-glass joints provide hermetic seals that protect the semiconductor from liquids and gases.

Compared with equivalent plastic packages, the TO-3 is more costly. The spacing and dimensions of the case leads make it unsuitable for higher frequency (radio frequency) devices.

Construction

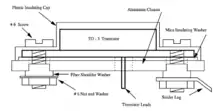

The semiconductor die component is mounted on a raised platform on a metal plate, with the metal can welded on top of it; providing high heat conductivity and durability. The metal case is connected to the internal device and the leads are connected to the die with bonding wires.

The TO-3 package consists of a diamond-shaped base plate with diagonals of 40.13 mm (1.580 in) and 27.17 mm (1.070 in). The plate has two mounting holes on the long diagonal, with the centers spaced 30.15 mm (1.187 in) apart.[5] The cap attached to one side of the plate brings the total height to up to 11.43 mm (0.450 in). Two pins on the other side of the plate are isolated from the package by individual glass-metal seals. The metal case forms the third connection (in the case of a bipolar junction transistor this is typically the collector).

Variants

TO-3 package variants for integrated circuits can have more than two leads. The height of the cap and the thickness of the leads differs between variants of the TO-3 package.

TO-41

The two pins of the TO-41 package end in soldering pads with holes in them to make it easier to solder wires to the pins for point-to-point construction (as opposed to soldering a TO-3 package on a printed circuit board). Otherwise the TO-41 package has the same dimensions as the TO-3 package.[6] Some variants of the TO-41 package have a third pin with a soldering pad connected to the case (e.g. AD133,[7]: 64 AUY21[7]: 69 ). This 3-pin package was standardized by IEC as C14B/B28.[7]: 215

TO-204

TO-204 is intended to replace previous definitions of flange-mounted packages with a 10.92 mm (0.430 in) pin spacing.[8][9] The different outlines are now defined as variants of TO-204: TO-3 is renamed to TO-204-AA, TO-41 to TO-204-AB. A new package with a reduced maximum height of 7.62 mm (0.300 in) is added as TO-204-AC. Two additional variants specify pins thicker than the original 1.02 mm (0.040 in) to allow higher currents: 1.27 mm (0.050 in) for TO-204-AD and 1.52 mm (0.060 in) for TO-204-AE.

National standards

| Standards organization | Standard | Designation for | |||

|---|---|---|---|---|---|

| TO-3 | TO-41 | – | – | ||

| JEDEC | JEP95[9] | TO-204-AA | TO-204-AB | TO-204-AC | TO-204-AD |

| IEC | IEC 60191[lower-alpha 1][7]: 215 | C14A/B18 | C14B/B18 | ||

| DIN | DIN 41872[10][11] | 3A2 | 3B2[lower-alpha 2] | ||

| EIAJ / JEITA | ED-7500A[lower-alpha 1][12] | TC-3/TB-3 | – | TC-3A/TB-3[lower-alpha 2] | – |

| British Standards | BS 3934[lower-alpha 1][13][14] | SO-5A/SB2-2 | SO-5B/SB2-2[lower-alpha 2] | ||

| Gosstandart | GOST 18472—88[15] | KT-9[lower-alpha 3] | – | – | KT-9B |

| Rosstandart | GOST R 57439[16] | KT-9C | |||

| Kombinat Mikroelektronik Erfurt | TGL 11811[17] | Eeb | – | Eea | – |

| TGL 26713/11[17] | L2A2 | – | L2A1 | – | |

- These standards have separate drawings for the package case and the base.

- The maximum height is 8.63 mm (0.340 in).

- Russian: КТ-9

Common components in a TO-3 package

Common voltage regulator integrated circuits:

Common transistors:

See also

References

- "JEDEC TO-3 package specification" (PDF). JEDEC. Archived from the original (PDF) on June 18, 2017.

- Bottom, Virgil (November 1992). "XIII Phoenix 1953–1958". FROM POSSUM HOLLER TO SINGAPORE The Autobiography of VIRGIL E. BOTTOM. Self published. p. 177. Archived from the original (DOC) on 2016-03-15. Retrieved 2022-08-22.

- Ward, Jack (2007). "Motorola 2N176". www.semiconductormuseum.com. Retrieved 2022-08-22.

- Greenburg, Ralph (2008). "Transistor Museum Oral History". www.semiconductormuseum.com. Retrieved 2021-07-14.

- Hubert Biagi. "Mounting Considerations for TO-3 Packages" (PDF). Burr-Brown. p. 3. Retrieved 2021-06-30.

- "TO-41" (PDF). JEDEC. Archived from the original (PDF) on 2016-04-10. Retrieved 2021-06-21.

- "Semiconductors" (PDF). Pro Electron. 1978. Retrieved 2021-06-17.

- "Index by Device Type of Registered Transistor Outlines (TO)". JEDEC Publication No. 95 (PDF). JEDEC. October 2010. Retrieved 2021-07-13.

- "Flange Mounted Header Family 0.430 Pin Spacing". JEDEC Publication No. 95 (PDF). JEDEC. November 1982. pp. 174–177. Retrieved 2021-07-13.

- "NPN Transistor for Powerful AF Output Stages 2N3055" (PDF). Siemens. Retrieved 2021-08-20.

- "Silicon NPN Power Transistor BU546" (PDF). Telefunken. Retrieved 2021-08-20.

- "EIAJ ED-7500A Standards for the Dimensions of Semiconductor Devices" (PDF). JEITA. 1996. Retrieved 2021-06-14.

- "Semiconductor and Photoelectric Devices" (PDF). Mullard. 1968. p. 539. Retrieved 2021-06-14.

- "Mullard Technical Handbook Book 1 Part 1" (PDF). Mullard. 1974. p. 516. Retrieved 2021-06-14.

- "ГОСТ 18472—88 ПРИБОРЫ ПОЛУПРОВОДНИКОВЫЕ - Основные размеры" [GOST 18472—88 Semiconductor devices - basic dimensions] (PDF) (in Russian). Rosstandart. 1988. p. 42. Retrieved 2021-06-17.

- "ПРИБОРЫ ПОЛУПРОВОДНИКОВЫЕ - Основные размеры" [Semiconductor devices - basic dimensions] (PDF) (in Russian). Rosstandart. 2017. pp. 50–52. Retrieved 2021-06-17.

- "TGL 26713/11: Gehäuse für Halbleiterbauelemente - Bauform L" (PDF) (in German). Leipzig: Verlag für Standardisierung. June 1988. Retrieved 2021-06-15.

- Kluwers Internationale Transistor Gids (4 ed.). Kluwer Technische Boeken B.V. 1991. p. 55. ISBN 9020125192.

External links

- TO-3 standard from JEDEC

- TO-3 package from EESemi.com

- Hermetic packages from National Semiconductor