Quilt packaging

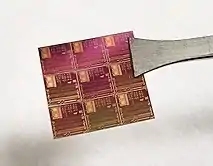

Quilt Packaging (QP) is an integrated circuit packaging and chip-to-chip interconnect packaging technology that utilizes “nodule” structures that extend out horizontally from the edges of microchips to make electrically and mechanically robust chip-to-chip interconnections.[1][2]

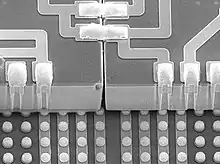

QP nodules are created as an integral part of the microchip using standard back end of the line semiconductor device fabrication techniques. Solder is then electroplated on top of the nodules to enable the chip to chip interconnection with sub-micron alignment accuracy.[3]

Small high yielding “chiplets” made from any semiconductor material (Silicon, Gallium Arsenide, Silicon Carbide, Gallium Nitride, etc.), can be “quilted” together to create larger multi-function meta-chip.[4] Thus, QP technology can integrate multiple chips with dissimilar technologies or substrate materials in planar, 2.5D and 3D configurations.[5]

RF Analog Performance

Multiple measured insertion loss on QP interconnects have been conducted on quilted chipsets with sets of homogeneous and heterogeneous semiconductor materials. Radio frequency S-parameter measurements were made from DC to 220 GHz. QP interconnects have demonstrated less than 0.1 dB insertion loss from DC to 100 GHz between silicon and silicon chips,[2] and less than 0.8 dB insertion loss up to 220 GHz between Silicon and Gallium Arsenide.[6]

Digital Performance

QP interconnects have a achieved 12 gigabit/sec (Gbps) bit-rate throughput with no distortion with 10 µm nodules on a 10 µm pitch on the edge of the chip.[7]

Optics/Photonics

Preliminary optical coupling loss simulations and measurements indicate that inter-chip coupling loss is < 6 dB for a gap of less than 4 µm. Loss rapidly improves as the gap approaches zero, which is achievable with Quilt Packaging assembly tolerances.[8][9]

References

- Zheng, Quanling; Kopp, David; Khan, Mohammad Ashraf; Fay, Patrick; Kriman, Alfred M.; Bernstein, Gary H. (March 2014). "Investigation of Quilt Packaging Interchip Interconnect With Solder Paste". IEEE Transactions on Components, Packaging and Manufacturing Technology. 4 (3): 400–407. doi:10.1109/tcpmt.2014.2301738. ISSN 2156-3950. S2CID 36676516.

- Ashraf Khan, M.; Zheng, Quanling; Kopp, David; Buckhanan, Wayne; Kulick, Jason M.; Fay, Patrick; Kriman, Alfred M.; Bernstein, Gary H. (2015-06-01). "Thermal Cycling Study of Quilt Packaging". Journal of Electronic Packaging. 137 (2). doi:10.1115/1.4029245. ISSN 1043-7398.

- Ahmed, Tahsin; Butler, Thomas; Khan, Aamir A.; Kulick, Jason M.; Bernstein, Gary H.; Hoffman, Anthony J.; Howard, Scott S. (2013-09-10). Sasián, José; Youngworth, Richard N. (eds.). "FDTD modeling of chip-to-chip waveguide coupling via optical quilt packaging". Optical System Alignment, Tolerancing, and Verification VII. SPIE. 8844: 88440C. Bibcode:2013SPIE.8844E..0CA. doi:10.1117/12.2024088. S2CID 120463545.

- Khan, M. Ashraf; Kulick, Jason M.; Kriman, Alfred M.; Bernstein, Gary H. (January 2012). "Design and Robustness of Quilt Packaging Superconnect". International Symposium on Microelectronics. 2012 (1): 000524–000530. doi:10.4071/isom-2012-poster_khan. ISSN 2380-4505.

- Sparkman, Kevin; LaVeigne, Joe; McHugh, Steve; Kulick, Jason; Lannon, John; Goodwin, Scott (2014-05-29). Holst, Gerald C.; Krapels, Keith A.; Ballard, Gary H.; Buford, James A.; Murrer, R. Lee (eds.). "Scalable emitter array development for infrared scene projector systems". Infrared Imaging Systems: Design, Analysis, Modeling, and Testing XXV. SPIE. 9071: 90711I. Bibcode:2014SPIE.9071E..1IS. doi:10.1117/12.2054360. S2CID 53508849.

- Fay, Patrick; Bernstein, Gary H.; Lu, Tian; Kulick, Jason M. (2016-04-29). "Ultra-wide Bandwidth Inter-Chip Interconnects for Heterogeneous Millimeter-Wave and THz Circuits". Journal of Infrared, Millimeter, and Terahertz Waves. 37 (9): 874–880. Bibcode:2016JIMTW..37..874F. doi:10.1007/s10762-016-0278-5. ISSN 1866-6892.

- Lu, Tian; Ortega, Carlos; Kulick, Jason; Bernstein, G. H.; Ardisson, Scott; Engelhardt, Rob (2016). "Rapid SoC prototyping utilizing quilt packaging technology for modular functional IC partitioning". Proceedings of the 27th International Symposium on Rapid System Prototyping: Shortening the Path from Specification to Prototype. New York, New York, USA: ACM Press. pp. 79–85. doi:10.1145/2990299.2990313. ISBN 978-1-4503-4535-4. S2CID 9121042.

- Ahmed, Tahsin; Khan, Aamir A.; Vigil, Genevieve; Kulick, Jason M.; Bernstein, Gary H.; Hoffman, Anthony J.; Howard, Scott S. (2014). "Optical Quilt Packaging: A New Chip-to-Chip Optical Coupling and Alignment Process for Modular Sensors". Cleo: 2014. Washington, D.C.: OSA: JTu4A.56. doi:10.1364/cleo_at.2014.jtu4a.56. ISBN 978-1-55752-999-2. S2CID 14432676.

- Ahmed, Tahsin; Lu, Tian; Butler, Thomas P.; Kulick, Jason M.; Bernstein, Gary H.; Hoffman, Anthony J.; Hall, Douglas C.; Howard, Scott S. (2017-05-01). "Mid-Infrared Waveguide Array Inter-Chip Coupling Using Optical Quilt Packaging". IEEE Photonics Technology Letters. 29 (9): 755–758. Bibcode:2017IPTL...29..755A. doi:10.1109/lpt.2017.2684091. ISSN 1041-1135. S2CID 7455544.