AMD K5

The K5 is AMD's first x86 processor to be developed entirely in-house. Introduced in March 1996, its primary competition was Intel's Pentium microprocessor. The K5 was an ambitious design, closer to a Pentium Pro than a Pentium regarding technical solutions and internal architecture. However, the final product was closer to the Pentium regarding performance, although faster clock-for-clock compared to the Pentium.

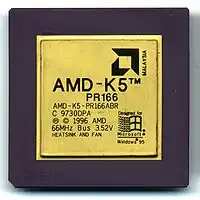

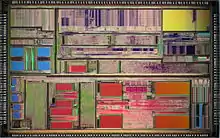

An AMD K5 PR166 microprocessor | |

| General information | |

|---|---|

| Launched | March 27, 1996 (SSA/5) October 7, 1996 (5k86) |

| Common manufacturer(s) | |

| Performance | |

| Max. CPU clock rate | 75 MHz to 133 MHz |

| FSB speeds | 50 MHz to 66 MHz |

| Cache | |

| L1 cache | 8 KB + 16 KB (data + instructions) |

| Architecture and classification | |

| Application | Desktop, Embedded |

| Microarchitecture | K5 |

| Instruction set | IA-32/x86 |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Socket(s) | |

| Products, models, variants | |

| Model(s) |

|

| History | |

| Predecessor(s) | Am5x86 |

| Successor(s) | K6 |

Technical details

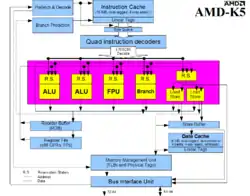

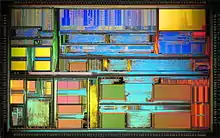

The K5 was based upon an internal highly parallel RISC processor architecture with an x86 decoding front-end.[1] The K5 offered good x86 compatibility and the in-house-developed test suite proved invaluable on later projects. All models had 4.3 million transistors, with five integer units that could process instructions out of order and one floating-point unit. The branch target buffer was four times the size of the Pentium's and register renaming helped overcome register dependencies.[2] The chip's speculative execution of instructions reduced pipeline stalls. It had a 16 KB four-way set-associative instruction cache and an 8 KB data cache. The floating-point divide and square-root microcode were mechanically proven.[3][4] The floating-point transcendental instructions were implemented in hardware and were faithful to true mathematical results for all operands.[5]

Performance

The K5 project represented an early chance for AMD to take technical leadership from Intel. Although the chip addressed the right design concepts, the actual engineering implementation had its issues. The low clock rates were, in part, due to AMD's limitations as a "cutting edge" manufacturing company at the time, and in part due to the design itself, which had many levels of logic for the process technology of the day, hampering clock scaling. Additionally, while the K5's floating-point performance was regarded as superior to that of the Cyrix 6x86, it was slower than that of the Pentium, although offering more reliable transcendental function results. Because it was late to market and did not meet performance expectations, the K5 never gained the acceptance among large computer manufacturers that the earlier Am486 and later AMD K6 enjoyed.

Features

Models

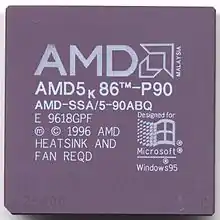

There were two revisions of the K5 architecture, internally called the SSA/5 and the 5k86, both released with the K5 label. The original set of "SSA/5" CPUs had its branch prediction unit disabled and additional internal waitstates added; these issues were remedied with the "5k86", resulting in up to 30% better performance clock for clock.[6][7] The "SSA/5" line ran from 75 to 100 MHz; the "5k86" line ran from 90 to 133 MHz. However, AMD used what it called a PR rating, or performance rating, to label the chips according to their suggested equivalence in integer performance to a Pentium of that clock speed. Thus, a 116 MHz chip from the second line was marketed as the "K5 PR166". Manufacturing delays caused the PR200's arrival to nearly align with the release of K6. Since AMD did not want the two chips competing, the K5-PR200 only arrived in small numbers.

SSA/5

- Sold as 5K86 P75 to P100, later as K5 PR75 to PR100

- 4.3 million transistors in 500 or 350 nm

- L1-Cache: 8 + 16 KB (data + instructions)

- Socket 5 and Socket 7

- VCore: 3.52 V

- Front side bus: 50 (PR75), 60 (PR90), 66 MHz (PR100)

- First release: March 27, 1996

- Clockrate: 75, 90, 100 MHz

5k86

- Sold as K5 PR120 to PR166; later PR200

- 4.3 million transistors in 350 nm

- L1-Cache: 8 + 16 KB (data + instructions)

- Socket 5 and Socket 7

- VCore: 3.52 V

- Front side bus: 60 (PR120/150), 66 MHz

- First release: October 7, 1996

- Clockrate: 90 (PR120), 100 (PR133), 105 (PR150), 116.6 (PR166), 133 MHz (PR200)

References

- AMD-K5 Processor Technical Reference Manual (PDF). AMD. November 1996.

- "AMD-K5 Processor Data Sheet" (PDF). AMD. January 1997.

- Moore, J. Strother; Lynch, Thomas W.; Kaufmann, Matt (September 1998). "A Mechanically Checked Proof of the AMD5K86TM Floating-Point Division Program". IEEE Transactions on Computers. Washington, DC, USA: IEEE Computer Society. 47 (9): 913–926. doi:10.1109/12.713311.

- Russinoff, David M. (January 1999). "A Mechanically Checked Proof of Correctness of the AMD K5 Floating Point Square Root Microcode". Formal Methods in System Design. Hingham, MA, USA: Kluwer Academic Publishers. 14 (1): 75–125. doi:10.1023/A:1008669628911. S2CID 22941018.

- Lynch, T.; Ahmed, A.; Schulte, M.; Callaway, T.; Tisdale, R. (19–21 July 1995). "The K5 Transcendental Functions". Proceedings of the 12th Symposium on Computer Arithmetic. Washington, DC, USA: IEEE Computer Society. pp. 163–170. doi:10.1109/ARITH.1995.465368. ISBN 0-8186-7089-4.

- "X86 CPU Reference (Part 2)". alasir.com. Archived from the original on 26 July 2017. Retrieved 12 January 2022.

- "Microprocessor History - AMD K5". May 2019.

Further reading

- Gwennap, Linley (25 March 1996). "AMD Ships Pentium Competitor". Microprocessor Report.

- Slater, Michael (24 October 1994). "AMD's K5 Designed to Outrun Pentium". Microprocessor Report.

- Slater, Michael (8 May 1995). "AMD K5 Volume Slips into 1996". Microprocessor Report.