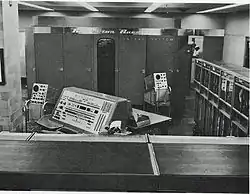

UNIVAC II

The UNIVAC II computer was an improvement to the UNIVAC I that the UNIVAC division of Sperry Rand first delivered in 1958. The improvements included the expansion of core memory from 2,000 to 10,000 words; UNISERVO II tape drives, which could use either the old UNIVAC I metal tapes or the new PET tapes; and some transistorized circuits (although it was still overwhelmingly a vacuum tube computer). It was fully compatible with existing UNIVAC I programs for both code and data. It weighed about 16,000 pounds (8.0 short tons; 7.3 t).

Circuit elements of entire system

| Tubes | 5,200 |

| Tube types | 20 |

| Crystal diodes | 18,000 |

| Magnetic cores | 184,000 |

| Transistors | 1,200 |

| Separate cabinets | 4 |

Above figures are approximate and do not include input-output devices.

Programming and numerical system

| Internal number system | Binary coded decimal |

| Decimal digits/word | 12 |

| Decimal digits/instruction | 6 |

| Instructions per word | 2 |

| Instructions decoded | 54 |

| Instructions used | 54 |

| Arithmetic system | Fixed point |

| Instruction type | One address |

| Number range between | -1 and +1 |

Decimal point occurs at the right of the sign digit.

Arithmetic unit

| Construction | Vacuum tubes |

| Arithmetic mode | Serial |

| Timing | Synchronous |

| Operation | Sequential |

| Including storage access (microseconds) | Excluding storage access (microseconds) | |

| Addition | 160 | 120 |

| Multiplication | 1,720 | 1,680 |

| Division | 3,030 | 2,990 |

Addition, subtraction, and multiplication times given below include reading and executing the instruction. The time includes formation of the result in the accumulator. All instructions, however are performed at minimum latency rates.

| Average operating speeds in microseconds | |

| Addition or subtraction | 200 (11-digit numbers) |

| Multiplication | 1,900 (11-digit numbers) |

| Division | 3,700 (11-digit numbers) |

| Comparison | 200 (12-digit numbers) |

| Transfer (memory to register or vice versa) | 40/word + 80/instruction |

Magnetic core

| Capacity | 10,000 words; 120,000 characters |

| Memory locations | 0000 - 1999 |

| Access time | Zero (memory references begin during "Time Out") |

| Basic cycle | 20 microseconds |

| Construction | 42 separate magnetic core planes, each one a rectangle 50 cores wide and 80 cores long. |

All users utilize a 2,000-word, 24,000-digit magnetic-core storage unit. Each of the planes is divided into two sections of 50 by 40 cores, making 2,000 cores in each section. Each section contains one core - for one binary position (bit) - of every one of the 2,000 words. The same relative binary position of the other half-word is held in a core in the same physical location in the other section of the plane. Thus each plane contains two binary positions in each of 2,000 words; the first and 43rd, for example, or the 9th and 52nd. Physically the memory is a rectangular prism 7.25×10×12.75 inches (18.4×25.4×32.4 cm).

A memory location thus always implies two cores in all 42 planes. The two cores are determined by the intersection of one column of fifty possible columns with two rows of the 80 possible rows. One row is in each section of the plane. All 42 planes are used twice for each word.

Associated with the memory is a half-word insertion register of 42-bit capacity. Each bit is temporarily stored in a magnetic core of this register during a memory reference. Each of these register cores is associated with one of the 42 memory planes. To write into the memory, the first half of the word is placed in the insertion register and the address selector alerts the appropriate column and the proper row of the top section in each of the 42 planes. At the appropriate instant the information is transferred from each core of the insertion register to the selected core in the corresponding plane of the memory. Forty-two pulse times later, the second half word has been placed in the insertion register and the process is repeated in the lower section of the memory. Read-outs are accomplished in a reverse manner. The speed of the memory has been adjusted to the speed of the arithmetic portion of the Univac which permits the transfer into or out of the memory of 12 characters in 40 microseconds. Word pulses flow from or to the high speed bus and the insertion register via a mechanism which converts from serial to parallel and vice versa, in 42-bit modules.

Checking features

Whenever feasible, registers and other circuits appear in duplicate. Their contents are continuously compared so that inconsistencies between the data in the identical units give an indication of faulty operation, and stall the computer. At this point, the instruction may be repeated. The pulse code used in the Univac System is so designed that all characters contain an odd number of pulses. At several strategic points within Univac, every character is checked for an odd number of pulses. An indication is given whenever an even number of pulses is detected, and the computer stalls. Other types of checking circuits cause Univac to stall when other types of errors occur.

An error occurs if reference to a non-existent memory address is attempted.

An odd-even error in the transfer rI to rM will result in a transfer stop and the location of the error (rI address) will be indicated. The 720 character count will be displayed on a modulus 100 counter.

"All ones" checker

In addition to the parity bits check on the high-speed bus, a second checker establishes that the invalid "all ones" character is not inadvertently created by a system fault. Input and output checkers also detect the invalid "all ones" character.

Built-in checking features are contained in the Card-to-Tape Converter, the Tape-to-Card Converter and the High Speed Printer.

Fusing

Univac is completely fused in order that faults may be isolated. Each bay has its own set of fuses in addition to main fuses on all DC and AC potentials. If a fuse blows, power is shut off and an indicator circuit shows in which bay the blown fuse is located, and a "flag" indicates the specific fuse.

Voltage monitoring

An automatic voltage-monitoring system continuously monitors all critical DC potentials giving an alarm if any moves outside the prescribed limits.

References

- Much of the text in this article was extracted directly from Universal Automatic Computer Model II, which is in the public domain as an original work of the United States Federal Government (US Army). It was published as "A Third Survey of Domestic Electronic Digital Computing Systems", Report No. 1115, March 1961, by Martin H. Weik, published by Ballistic Research Laboratories, Aberdeen Proving Ground, Maryland. Department of the Army Project No. 5803-06-002.