NVAX

The NVAX is a CMOS microprocessor developed and produced by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). A variant of the NVAX, the NVAX+, differed in the bus interface and external cache supported, but was otherwise identical in regards to microarchitecture. The NVAX+ was designed to have the same bus as the DECchip 21064, allowing drop-in replacement.

The NVAX and NVAX+ was used in late-model VAX systems released in 1991 such as the MicroVAX 3100, VAXstation 4000, VAX 4000, VAX 6000, VAX 7000/10000 and VAXft. Although Digital updated the design throughout the early 1990s, the processors, and the VAX platform itself, were ultimately superseded by the introduction of the DECchip 21064, an implementation of the Alpha (then Alpha AXP) architecture, and the resulting systems in November 1992.

The NVAX was offered at a variety of clock speeds, 83.3 MHz (12 ns), 71 MHz (14 ns) and 62.5 MHz (16 ns), while the NVAX+ is clocked at a frequency of 90.9 MHz (11 ns). The NVAX offered about 25 VAX Unit of Performance (VUPs), while the NVAX+ was roughly 35 VUPs. This was only slightly less than the VAX 9000 mainframe's roughly 40 VUPs, but available in a desktop form factor.

The final model in the series was the NVAX++, or NV5, offering 50 VUPs. This was the last VAX processor, DEC had moved entirely to the DEC Alpha after that point.

Description

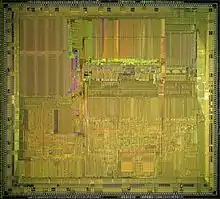

NVAX contained 1.3 million transistors on a die measuring 16.2 by 14.6 mm in size (236.52 mm²). The die was fabricated in Digital's fourth-generation CMOS process, CMOS-4, a 0.75 µm process with three layers of aluminium interconnect. The NVAX is packaged in a 339-pin pin grid array. The NVAX was offered at a variety of clock speeds, 83.3 MHz (12 ns), 71 MHz (14 ns) and 62.5 MHz (16 ns), while the NVAX+ is clocked at a frequency of 90.9 MHz (11 ns). The NVAX offered about 25 VAX Unit of Performance (VUPs).

The NVAX+, introduced at the same time, was identical in terms of the processor design but used a different bus, cache system and its external connection was a 431-pin array. These were identical to those on the Alpha, allowing an NVAX+ machine to be upgraded to an Alpha simply by changing the CPU. These changes also allowed it to operate with slightly higher performance, and the NVAX+ ran at roughly 35 VUPs. This was only slightly less than the VAX 9000 mainframe's roughly 40 VUPs.

In 1994, the NVAX++ (also known as NV5) was introduced in VAX 7000 Model 7x0 and VAX 10000 Model 7x0 systems. It operated at 133 MHz (7.5 ns) and was fabricated in Digital's fifth-generation CMOS process, CMOS-5, a 0.50 µm process. It improved performance to 50 VUPs. In 1996, a 170.9 MHz NV5 was introduced, used in the VAX 7000/10000 Model 8x0.

Microarchitecture

The NVAX is partitioned into five semi-autonomous units, the I-box, E-box, F-box, M-box and C-box. The NVAX is macropipelined. Multiple VAX macroinstructions are processed in parallel by autonomous units, which have their own micropipelines.

The I-box fetches and decodes VAX instructions. It also contains the 2 KB direct-mapped virtual instruction cache (VIC) and the 512-entry by 4-bit branch history table. The I-box aimed to fetch eight bytes of instruction data from the VIC during every cycle.

The E-box executes most non-floating-point instructions. It is controlled by microcode from a 1,600-word control store with the capability to patch 20 words.

The F-box executes floating-point instructions as well as 32-bit integer multiply instructions. It has a four-stage floating-point and integer multiply pipeline and a non-pipelined floating-point divider.

References

- Uhler, Michael G. et al. "The NVAX and NVAX+ High-performance VAX Microprocessors" Archived 2014-11-29 at the Wayback Machine. Digital Technical Journal, Volume 4, Number 3, Summer 1992. pp. 11–23.

- Nuessgen, Marco. "VAX CPU Model Summary".

Further reading

- Digital Technical Journal: special issue on NVAX-microprocessor VAX systems. (Digital Equipment Corporation)4 (3). Summer 1992. ISSN 0898-901X.

- Anderson, W. (1992). "Logical verification of the NVAX CPU chip design". Proceedings 1992 IEEE International Conference on Computer Design: VLSI in Computers & Processors. pp. 306–309. ISBN 0-8186-3110-4.

- Badeau, R.W. et al. (1992). "A 100-MHz macropipelined VAX microprocessor". IEEE Journal of Solid-State Circuits, Volume 27, Issue 11. pp. 1585–1598. ISSN 0018-9200.

- Fox, Thomas F. (1994). "The design of high-performance microprocessors at Digital". Proceedings of the 31st Annual ACM-IEEE Design Automation Conference. pp. 586–591.