Intel X58

The Intel X58 (codenamed Tylersburg) is an Intel chip designed to connect Intel processors with Intel QuickPath Interconnect (QPI) interface to peripheral devices. Supported processors implement the Nehalem microarchitecture and therefore have an integrated memory controller (IMC), so the X58 does not have a memory interface. Initially supported processors were the Core i7,[1] but the chip also supported Nehalem and Westmere-based Xeon processors.

| Codename(s) | Tylersburg |

|---|---|

| CPU supported | |

| Socket supported | LGA 1366 |

| Fabrication process | 65 nm |

| Southbridge(s) | ICH10 |

| Miscellaneous | |

| Release date(s) | November 2008 |

| Predecessor |

|

| Successor | Intel X79 (Patsburg PCH) |

Description

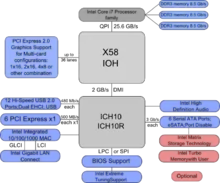

The QuickPath architecture differs considerably from earlier Intel architectures, and is much closer to AMD's HyperTransport architecture. Except for the lack of a memory interface, the X58 is similar to the traditional northbridge: it communicates with the processor(s) via the high bandwidth QuickPath Interconnect, it communicates with the southbridge via Direct Media Interface (DMI), and it communicates with high bandwidth peripherals via PCI Express (PCIe).

The X58 is not a memory controller hub (MCH), because it has no memory interface, so Intel calls it an I/O hub. This should not be confused with the similar term I/O controller hub (ICH) which has traditionally been used to refer to the southbridge chips. Intel documentation now refers to the southbridge as the Legacy I/O Controller Hub.

The X58 has 36 PCIe lanes that are arranged in two ×16 links, DMI link and "spare"-based link. When used with the ICH10 I/O Controller Hub with ×4 DMI connection the "spare" supports a separate ×4 PCIe connection. Future southbridge chips DMI may support a wider DMI.

Each X58 QuickPath Interconnect uses 21 unidirectional differential pairs in each direction, for a total of 84 pins per QPI. At the highest bandwidth, each QPI can transfer up to 12.8 GB/s usable in each direction simultaneously using the QPI protocol. The protocol transfers information in 80 bit flits which contain 8 bits of error correction, 8 bits of QPI routing information, and 64 bits of data.

X58 PCIe ports support full PCIe 2.0 bandwidth (e.g., up to 8GB/s including overheads per ×16 link) and each ×16 link may be divided into total 16 lanes in any combination of ×8, ×4, ×2 or ×1 ports. They also support all features of line-reserved wiring, which means that in the combinations of (×16 + ×1/×8) slots, often used on the motherboards, not only ×1 or ×8 cards may be installed into the ×1/×8 slot, but ×4 cards should work as well (if not disallowed by the motherboard BIOS.)

Unlike the front-side bus (FSB), QPI is a point-to-point interface and supports not only processor-chipset interface, but also processor-to-processor connection and chip-to-chip connection. The X58 has two QPIs and can directly connect to two processors on a multi-socket motherboard or form a ring-like connection (processor 1 to X58 to processor 2 back to processor 1). When used with the Intel Core i7, the second QPI is usually unused (though, in principle, the second X58 might be daisy-chained on the board).

When used with the "Gainestown" DP processor, which will have two QPIs, the X58 and the two processors may be connected in a triangle or ring. For MP processors such as "Beckton" with more than two QPIs, the X58 is either connected to two processors, which in turn are connected in a "mesh" of QPIs to other processors or attached "in pairs" to two different processors. I/O for "remote" processors is relayed via the inter-processors QPI.

X58 board manufacturers can build SLI-compatible Intel chipset boards by submitting their designs to nVidia for validation. However, users wishing to run more than two Nvidia video cards in PCIe ×16 will still need to purchase motherboards equipped with one or more nVidia nForce chipsets. It is still possible to run more than two video cards in an SLI-configuration at fewer PCIe lane widths.[2] The X58 chipset itself supports up to 36 PCI-Express 2.0 lanes, so it is possible to have two PCIe ×16 slots and one PCIe ×4 slot on the same motherboard.[1]

Interfaces

- QPI (Intel QuickPath Interconnect)[3]

- PCI Express 2.0

- ICH10-compatible DMI.

See also

References

- "Nehalem and X58 show up in Taipei". bit-tech.net. May 30, 2008. Archived from the original on June 22, 2008.

- "Hell Freezes Over: NVIDIA Announces Native SLI Support for the Intel X58 Chipset". AnandTech. August 28, 2008.

- "Nehalem desktop platform planning". HKEPC. January 3, 2008.