MOS Technology 8563

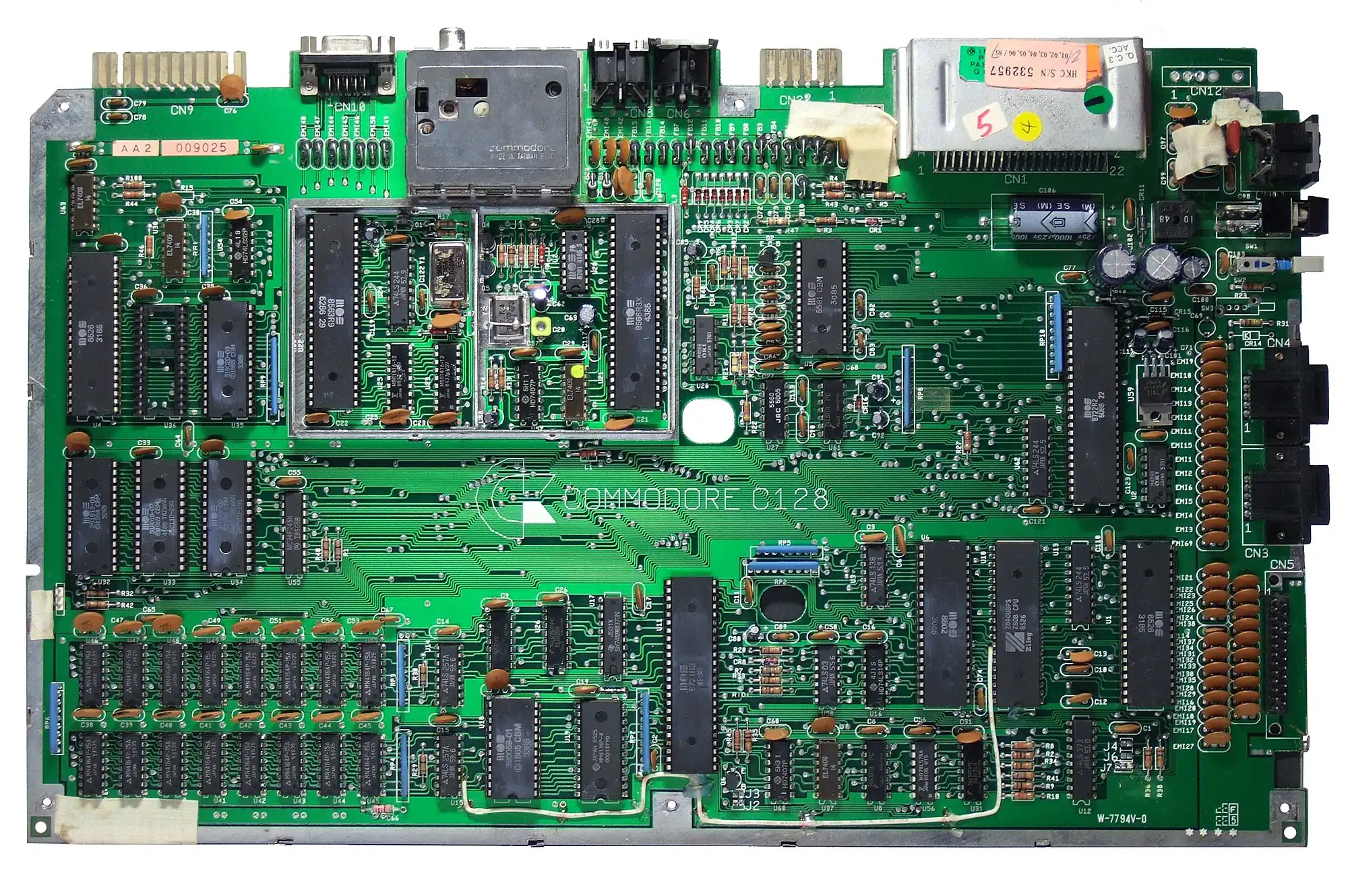

The 8563 Video Display Controller (VDC) was an integrated circuit produced by MOS Technology. It was used in the Commodore 128 (C128) computer to generate an 80-column (640 × 200 pixel) RGB video display, running alongside a VIC-II which supported Commodore 64-compatible graphics. The DCR models (as well as a few D-models) of the C128 used the later and more technically advanced 8568 [D]VDC controller.

History and characteristics

Originally intended for a planned (but unreleased) UNIX-based business computer based around the Zilog Z8000, Commodore designed the VDC into several prototype machines. Of these, only the Commodore 128 ever saw production. Unlike earlier MOS video chips such as the popular VIC-II, the VDC had dedicated video memory, 16 kilobytes (16,384 bytes; upgradable to 64 kilobytes, 65,536 bytes) in the original or "flat" C128 and 64 kilobytes in the C128DCR. This RAM was not directly accessible by the microprocessor.

The 8563 was more difficult to produce than most of the rest of the MOS Technology line, and initial yields were very low. The early units also had significant reliability problems and tended to self-destruct from overheating.[1] Also, there were timing issues with the VDC that would cause indirect load and store operations on its registers to malfunction.

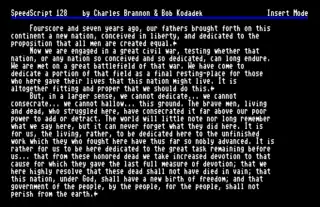

Officially, the VDC was a text-only chip, although a careful reading of the technical literature by MOS Technology that was given to the early C128 developers did indicate that a high-resolution bitmap mode was possible—it simply wasn't described in any detail. BASIC 7.0, the C128's built-in programming language, only supported high-resolution graphics in 40-column mode via the legacy VIC-II chip.

Shortly after the release of the C128 the VDC's bitmap mode was described in considerable detail in the Data Becker book "Commodore 128 - Das große GRAFIK-Buch" (published in late 1985 in the United States by Abacus Software), and an assembly language program was provided by the German authors Klaus Löffelmann and Dieter Vüllers, in which it was possible to set or clear any pixel or, using BASIC to perform the necessary calculations, generate bitmapped geometric shapes on the 80 column screen.[2] In February 1986, less than a year after the Commodore 128's release, RUN magazine published "Ultra Hi-Res Graphics", an article describing the VDC's bitmapped mode and including a type-in program (written in 8502 assembly language) that extended BASIC 7.0's capabilities to support 640×200 high-resolution graphics using the 8563. Authors Lou Wallace and David Darus later developed the Ultra Hi-Res utility into a commercial package, BASIC 8. One of the most popular third-party utilities for the C128, this offered more advanced VDC high-resolution capabilities to a wide audience of programmers.

Commodore finally offered complete official documentation on the VDC in the Commodore 128 Programmer's Reference Guide. VDC bitmap modes were used extensively in the C128 version of the GEOS operating system.

The VDC lacked sprite capabilities, which limited its use in gaming applications. However, it did contain blitting capabilities to autonomously perform small block memory copies within its dedicated video RAM. While the VDC is performing such a copy, the system CPU can continue running code, provided no other VDC accesses are attempted before the copy is finished. These functions were used by the C128's screen editor ROM to rapidly scroll or clear screen sections.

Technical specifications

- RGBI output (RGB plus Intensity) compatible with IBM's CGA video standard.*

- 16 or 64 kilobyte address space for display, character shape and display attribute memory (dedicated, separate from system memory).

- Up to 720 × 700 pixel video resolution in interlaced mode (maximum with 64 kilobyte video RAM). Other image sizes are possible, depending on programmer's needs, such as 640 × 200 non-interlaced, 640 × 400 interlaced, etc.

- 80 × 25 characters text resolution (C128 kernal default); other sizes such as 80 × 50 or 40 × 25 are possible.

- 8 colors at 2 intensities.

* This applies to US 60 Hz C128s only. 50 Hz C128 machines output a signal with a 50 Hz vertical refresh. Although not conforming to the CGA standard, most CGA monitors were capable of displaying the 50 Hz signal without problems. However, some monitors either failed to resolve the signal or succeeded in resolving it, but sooner or later their deflection circuits would fail due to electrical or thermal stress, requiring repair.

Programming

Addressing the VDC's internal registers and dedicated video memory must be accomplished by indirect means. First the program must tell the VDC which of its 37 internal registers is to be accessed. Next the program must wait until the VDC is ready for the access, after which a read or write on the selected internal register may be performed. The following assembly code is typical of a register read:

ldx #regnum ;VDC register to access

stx $d600 ;write to control register

loop bit $d600 ;check bit 7 of status register

bpl loop ;VDC not ready

lda $d601 ;read from VDC register

...

The following code is typical of a register write operation:

ldx #regnum ;VDC register to write to

stx $d600 ;write to control register

loop bit $d600 ;check bit 7 of status register

bpl loop ;VDC not ready

sta $d601 ;write to VDC register

...

The same is feasible in BASIC language, calling specific KERNAL routines :

This code is typical of a VDC register read, where ⟨register⟩ it's a number between 0 and 36, as show below.

BANK15

...

SYS DEC("CDDA"),, register : RREG VDC

REM $ccda aka 52698 in decimal

PRINT VDC

...

this code is typical of a VDC register write, where ⟨register⟩ it's a number between 0 and 36, and ⟨value⟩ it's a number between 0 and 255, that you wish to place in that register.

BANK15

...

SYS DEC("CDCC"), value, register

REM $ccdc aka 52684 in decimal

...

Owing to this somewhat cumbersome method of controlling the VDC, the maximum possible frame rate in bitmapped mode is generally too slow for arcade-style action video games, in which bit-intensive manipulation of the display is required.

In standard text mode, the VDC behaves much like the VIC-II except with 2k of screen memory instead of 1k. The power on default configuration places screen memory in $0-$7FF and the

color memory at $800-$9FF and they can be moved anywhere in VDC memory as long as it's on a 2k boundary. Attributes are handled like the VIC-II's high resolution mode with a global background color and each character foreground color set individually per the color RAM. In addition to color data, the latter also contains attribute data for each character. Bit 4 causes the character to blink if enabled, Bit 5 produces underlined characters, and Bit 6 inverts the character's bitmap pattern. Bit 7 enables the alternate character set. The VDC can use as many as 512 characters. When the alternate character flag for a given character is enabled, the character pattern will be drawn from characters 256–511. Thus if character 65 is displayed, enabling the alternate character flag will display character 321 instead. The alternate character flag is normally used when upper/lowercase mode is set—the flag is enabled for all VDC screen positions, causing the upper/lowercase character set and its reverse video versions to be displayed instead of the default uppercase/graphics character set.

The VDC does not use a character ROM, instead the VIC-II's character ROM patterns are simply copied into VDC RAM as part of the C128's power on initialization including the patterns for reverse video characters even though the VDC is capable of inverting characters in hardware. Character patterns take 16 bytes instead of 8 to store as the VDC has adjustable character height. Since the screen is 25 lines, in practice character height is limited to 8 lines meaning that half the space for character data is left unused and wasted. The power on default configuration places the character data in $2000-$3FFF. $2000-$23FF contain the patterns for the uppercase/graphics characters, $2C00-$33FF the upper/lowercase characters, while $2400-$2BFF and $3400-$3FFF contain the reverse video patterns for each set. The user may freely define any custom characters and map them into VDC memory.

Register listing

This information was adapted from the Commodore 128 Programmer's Reference Guide[3]

| Register | Hexadecimal | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Description |

|---|---|---|---|---|---|---|---|---|---|---|

0 |

$00 |

HT7 |

HT6 |

HT5 |

HT4 |

HT3 |

HT2 |

HT1 |

HT0 |

Horizontal Total |

1 |

$01 |

HD7 |

HD6 |

HD5 |

HD4 |

HD3 |

HD2 |

HD1 |

HD0 |

Horizontal Displayed |

2 |

$02 |

HP7 |

HP6 |

HP5 |

HP4 |

HP3 |

HP2 |

HP1 |

HP0 |

Horizontal Sync Position |

3 |

$03 |

VW3 |

VW2 |

VW1 |

VW0 |

HW3 |

HW2 |

HW1 |

HW0 |

Vertical/Horizontal Sync Width |

4 |

$04 |

VT7 |

VT6 |

VT5 |

VT4 |

VT3 |

VT2 |

VT1 |

VT0 |

Vertical Total |

5 |

$05 |

— | — | — | VA4 |

VA3 |

VA2 |

VA1 |

VA0 |

Vertical Adjust |

6 |

$06 |

VD7 |

VD6 |

VD5 |

VD4 |

VD3 |

VD2 |

VD1 |

VD0 |

Vertical Displayed |

7 |

$07 |

VP7 |

VP6 |

VP5 |

VP4 |

VP3 |

VP2 |

VP1 |

VP0 |

Vertical Sync Position |

8 |

$08 |

— | — | — | — | — | — | IM1 |

IM0 |

Interlace Mode |

9 |

$09 |

— | — | — | — | CTV4 |

CTV3 |

CTV2 |

CTV1 |

Character Total Vertical |

10 |

$0A |

— | CM1 |

CM0 |

CS4 |

CS3 |

CS2 |

CS1 |

CS0 |

Cursor Mode, Start Scan |

11 |

$0B |

— | — | — | CE4 |

CE3 |

CE2 |

CE1 |

CE0 |

Cursor End Scan Line |

12 |

$0C |

DS15 |

DS14 |

DS13 |

DS12 |

DS11 |

DS10 |

DS9 |

DS8 |

Display Start Address High Byte |

13 |

$0D |

DS7 |

DS6 |

DS5 |

DS4 |

DS3 |

DS2 |

DS1 |

DS0 |

Display Start Address Low Byte |

14 |

$0E |

CP15 |

CP14 |

CP13 |

CP12 |

CP11 |

CP10 |

CP9 |

CP8 |

Cursor Position High Byte |

15 |

$0F |

CP7 |

CP6 |

CP5 |

CP4 |

CP3 |

CP2 |

CP1 |

CP0 |

Cursor Position Low Byte |

16 |

$10 |

LPV7 |

LPV6 |

LPV5 |

LPV4 |

LPV3 |

LPV2 |

LPV1 |

LPV0 |

Light Pen Vertical Position |

17 |

$11 |

LPH7 |

LPH6 |

LPH5 |

LPH4 |

LPH3 |

LPH2 |

LPH1 |

LPH0 |

Light Pen Horizontal Position |

18 |

$12 |

UA15 |

UA14 |

UA13 |

UA12 |

UA11 |

UA10 |

UA9 |

UA8 |

Update Address High Byte |

19 |

$13 |

UA7 |

UA6 |

UA5 |

UA4 |

UA3 |

UA2 |

UA1 |

UA0 |

Update Address Low Byte |

20 |

$14 |

AA15 |

AA14 |

AA13 |

AA12 |

AA11 |

AA10 |

AA9 |

AA8 |

Attribute Start Address High Byte |

21 |

$15 |

AA7 |

AA6 |

AA5 |

AA4 |

AA3 |

AA2 |

AA1 |

AA0 |

Attribute Start Address Low Byte |

22 |

$16 |

CTH3 |

CTH2 |

CTH1 |

CTH0 |

CDH3 |

CDH2 |

CDH1 |

CDH0 |

Character Total Horizontal, Character Display Horizontal |

23 |

$17 |

— | — | — | CDV4 |

CDV3 |

CDV2 |

CDV1 |

CDV0 |

Character Display Vertical |

24 |

$18 |

COPY |

RVS |

CBRATE |

VSS4 |

VSS3 |

VSS2 |

VSS1 |

VSS0 |

Vertical Smooth Scrolling |

25 |

$19 |

TEXT |

ATR |

SEMI |

DBL |

HSS3 |

HSS2 |

HSS1 |

HSS0 |

Horizontal Smooth Scrolling |

26 |

$1A |

FG3 |

FG2 |

FG1 |

FG0 |

BG3 |

BG2 |

BG1 |

BG0 |

Foreground/Background color |

27 |

$1B |

AI7 |

AI6 |

AI5 |

AI4 |

AI3 |

AI2 |

AI1 |

AI0 |

Address Increment per Row |

28 |

$1C |

CB15 |

CB14 |

CB13 |

RAM |

— | — | — | — | Character Base Address |

29 |

$1D |

— | — | — | UL4 |

UL3 |

UL2 |

UL1 |

UL0 |

Underline Scan Line |

30 |

$1E |

WC7 |

WC6 |

WC5 |

WC4 |

WC3 |

WC2 |

WC1 |

WC0 |

Word Count |

31 |

$1F |

DA7 |

DA6 |

DA5 |

DA4 |

DA3 |

DA2 |

DA1 |

DA0 |

Data Register |

32 |

$20 |

BA15 |

BA14 |

BA13 |

BA12 |

BA11 |

BA10 |

BA9 |

BA8 |

Block Start Address High Byte |

33 |

$21 |

BA7 |

BA6 |

BA5 |

BA4 |

BA3 |

BA2 |

BA1 |

BA0 |

Block Start Address Low Byte |

34 |

$22 |

DEB7 |

DEB6 |

DEB5 |

DEB4 |

DEB3 |

DEB2 |

DEB1 |

DEB0 |

Display Enable Begin |

35 |

$23 |

DEE7 |

DEE6 |

DEE5 |

DEE4 |

DEE3 |

DEE2 |

DEE1 |

DEE0 |

Display Enable End |

36 |

$24 |

— | — | — | — | DRR3 |

DRR2 |

DRR1 |

DRR0 |

DRAM Refresh Rate |

References

- "Commodore.ca | Products | Commodore 128, 128D, 128DCR, History, Manuals, Pictures & Time Line". www.commodore.ca. Archived from the original on 2003-07-26.

- Chapter 3.9.1 "VDC HI-RES-Grafik" Page 213ff

- Commodore Capital, Inc., (1986). Commodore 128 programmer's reference guide. New York, NY: Bantam Books, Inc.