Like NOR gates, NAND gates are so-called "universal gates" that can be combined to form any other kind of logic gate. Today, integrated circuits are not constructed exclusively from a single type of gate. Instead, EDA tools are used to convert the description of a logical circuit to a netlist of complex gates (standard cells) or transistors (full custom approach)

Standard gates constructions with a NOR gates combination

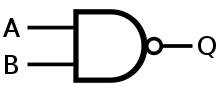

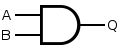

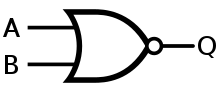

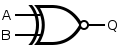

NAND

This is a NAND gate: trivially, just a NAND gate is used to realise it:

| Desired Gate | NAND Construction | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | ||||||||||||||||

| |||||||||||||||||

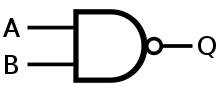

NOT

A NOT gate is made by joining the inputs of a NAND gate. Since a NAND gate is equivalent to an AND gate followed by a NOT gate, joining the inputs of a NAND gate leaves only the NOT part.

| Desired Gate | NAND Construction | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

|  | |||||||||

| ||||||||||

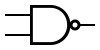

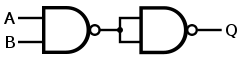

AND

An AND gate is made by following a NAND gate by a NOT gate as shown below. This gives a NOT NAND, i.e. AND.

| Desired Gate | NAND Construction | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | ||||||||||||||||

| |||||||||||||||||

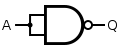

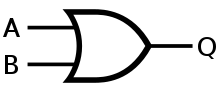

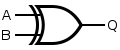

OR

If the truth table for a NAND gate is examined, it can be seen that if any of the inputs are 0, then the output will be 1. However to be an OR gate, if any input is 1, the output must also be 1. Therefore, if the inputs are inverted, any high input will trigger a high output.

| Desired Gate | NAND Construction | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | ||||||||||||||||

| |||||||||||||||||

NOR

A NOR gate is simply an OR gate with an inverted output:

| Desired Gate | NAND Construction | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | ||||||||||||||||

| |||||||||||||||||

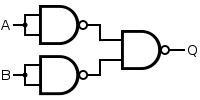

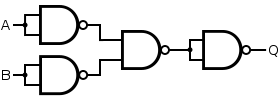

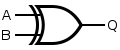

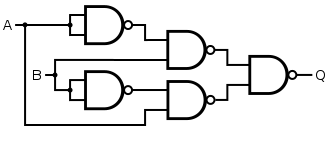

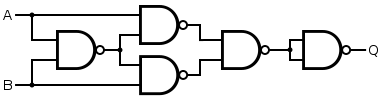

XOR

An XOR gate can be constructed from four NAND gates implementing the expression (A NAND N) NAND (B NAND N) where N = A NAND B. This construction entails a propagation delay three times that of a single NAND gate and uses four gates.

| Desired Gate | NAND Construction | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | ||||||||||||||||

| |||||||||||||||||

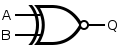

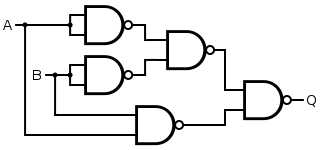

Alternatively, an XOR gate is made by considering the disjunctive normal form , noting from de Morgan's Law that a NAND gate is an inverted-input OR gate. This construction uses five gates instead of four.

| Desired Gate | NAND Construction |

|---|---|

|  |

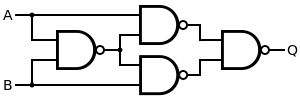

XNOR

An XNOR gate is made by considering the disjunctive normal form , noting from de Morgan's Law that a NAND gate is an inverted-input OR gate. This construction entails a propagation delay three times that of a single NAND gate and uses five gates.

| Desired Gate | NAND Construction | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | ||||||||||||||||

| |||||||||||||||||

Alternatively, the 4-gate version of the XOR gate can be used with an inverter. This construction has a propagation delay four times (instead of three times) that of a single NAND gate.

| Desired Gate | NAND Construction |

|---|---|

|  |

See also

- NOR logic. Like NAND gates, NOR gates are also universal gates.