Self-aligned gate

In semiconductor electronics fabrication technology, a self-aligned gate is a transistor manufacturing approach whereby the gate electrode of a MOSFET (metal–oxide–semiconductor field-effect transistor) is used as a mask for the doping of the source and drain regions. This technique ensures that the gate is naturally and precisely aligned to the edges of the source and drain.

The use of self-aligned gates in MOS transistors is one of the key innovations that led to the large increase in computing power in the 1970s. Self-aligned gates are still used in most modern integrated circuit processes.

Introduction

IC construction

Integrated circuits (ICs, or "chips") are produced in a multi-step process that builds up multiple layers on the surface of a disk of silicon known as a "wafer". Each layer is patterned by coating the wafer in photoresist and then exposing it to ultraviolet light being shone through a stencil-like "mask". Depending on the process, the photoresist that was exposed to light either hardens or softens, and in either case, the softer parts are then washed away. The result is a microscopic pattern on the surface of the wafer where a portion of the top layer is exposed while the rest is protected under the remaining photoresist.

The wafer is then exposed to a variety of processes that add or remove materials from the portions of the wafer that are unprotected by the photoresist. In one common process, the wafer is heated to around 1000 C and then exposed to a gas containing a doping material (commonly boron or phosphorus) that changes the electrical properties of the silicon. This allows the silicon to become an electron donor, electron receptor, or near-insulator depending on the type and/or amount of the dopant. In a typical IC this process is used to produce the individual transistors that make up the key elements of an IC.

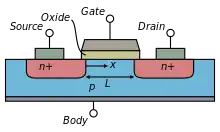

In the MOSFET, the three parts of a transistor are the source, the drain, and the gate (see diagram). The "field effect" in the name refers to changes to the conductivity that occur when a voltage is placed on the gate. The key point is that this electric field can cause the "channel" region separating the source and drain to become the same type as the source-drain, thus turning the transistor "on". Because no current flows from the gate to the drain, the switching energy of a FET is very small compared to earlier bipolar junction transistor types where the gate (or base as it was known) was in-line with the current.

Older methodology

In early MOSFET fabrication methodologies, the gate was made of aluminum which melts at 660 C, so it had to be deposited as one of the last steps in the process after all the doping stages had been completed at around 1000 C.

The wafer as a whole is first chosen to have a particular electrical quality as biased either positive, or "p", or negative, "n". In the illustration the base material is "p" (called n-channel or nMOS). A mask is then used to produce areas where the negative "n" sections of the transistors will be placed. The wafer is then heated to around 1000 C, and exposed to a doping gas that diffuses into the surface of the wafer to produce the "n" sections. A thin layer of insulator material (silicon dioxide) is then grown on top of the wafer. Finally, the gate is patterned on top of the insulating layer in a new photo-lithographic operation. To ensure the gate actually overlaps the underlying source and drain, the gate material has to be wider than the gap between the n sections, typically as much as three times. This wastes space and creates extra capacitance between the gate and the source-drain. This parasitic capacitance requires that the entire chip be driven at high power levels to ensure clean switching which is inefficient. Additionally, the variation in the misalignment of the gate to the underlying source-drain means that there is high chip-to-chip variability even when they are working properly.

Self-alignment

The self-aligned gate developed in several steps to its present form. Key to the advance was the discovery that heavily doped poly-silicon was conductive enough to replace aluminum. This meant the gate layer could be created at any stage in the multi-step fabrication process.[1]: p.1 (see Fig. 1.1)

In the self-aligned process, the key gate-insulating layer is formed near the beginning of the process. Then the gate is deposited and patterned on top. Then the source-drains are doped (for poly-silicon the gates are doped simultaneously). The source-drain pattern thus represents only the outside edges of the source and drain, the inside edge of those sections being masked by the gate itself. As a result, the source and drain "self-align" to the gate. Since they are always perfectly positioned, there is no need to make the gate wider than desired, and the parasitic capacitance is greatly reduced. Alignment time and chip-to-chip variability are likewise reduced.[2]

After early experimentation with different gate materials using aluminum, molybdenum and amorphous silicon, the semiconductor industry almost universally adopted self-aligned gates made with polycrystalline silicon (poly-silicon), the so-called silicon-gate technology (SGT) or "self-aligned silicon-gate" technology, which had many additional benefits over the reduction of parasitic capacitances. One important feature of SGT was that the transistor was entirely buried under top quality thermal oxide (one of the best insulators known), making it possible to create new device types, not feasible with conventional technology or with self-aligned gates made with other materials. Particularly important are charge-coupled devices (CCD), used for image sensors, and non-volatile memory devices using floating silicon-gate structures. These devices dramatically enlarged the range of functionality that could be achieved with solid state electronics.

Certain innovations were required in order to make self-aligned gates:[3]

- a new process that would create the gates;

- a switch from amorphous silicon to polycrystalline silicon (because amorphous silicon would break where it passed over "steps" in the oxide insulating surface);

- a photolithography method for etching polycrystalline silicon;

- a method to reduce the impurities present in silicon.

Prior to these innovations, self-aligned gates had been demonstrated on metal-gate devices, but their real impact was on silicon-gate devices.

History

The aluminum-gate MOS process technology started with the definition and doping of the source and drain regions of MOS transistors, followed by the gate mask that defined the thin-oxide region of the transistors. With additional processing steps, an aluminum gate would then be formed over the thin-oxide region completing the device fabrication. Due to the inevitable misalignment of the gate mask with respect to the source and drain mask, it was necessary to have a fairly large overlap area between the gate region and the source and drain regions, to ensure that the thin-oxide region would bridge the source and drain, even under worst-case misalignment. This requirement resulted in gate-to-source and gate-to-drain parasitic capacitances that were large and variable from wafer to wafer, depending on the misalignment of the gate oxide mask with respect with the source and drain mask. The result was an undesirable spread in the speed of the integrated circuits produced, and a much lower speed than theoretically possible if the parasitic capacitances could be reduced to a minimum. The overlap capacitance with the most adverse consequences on performance was the gate-to-drain parasitic capacitance, Cgd, which, by the well-known Miller effect, augmented the gate-to-source capacitance of the transistor by Cgd multiplied by the gain of the circuit to which that transistor was a part. The impact was a considerable reduction in the switching speed of transistors.

In 1966, Robert W. Bower realized that if the gate electrode was defined first, it would be possible not only to minimize the parasitic capacitances between gate and source and drain, but it would also make them insensitive to misalignment. He proposed a method in which the aluminum gate electrode itself was used as a mask to define the source and drain regions of the transistor. However, since aluminum could not withstand the high temperature required for the conventional doping of the source and drain junctions, Bower proposed to use ion implantation, a new doping technique still in development at Hughes Aircraft, his employer, and not yet available at other labs. While Bower’s idea was conceptually sound, in practice it did not work, because it was impossible to adequately passivate the transistors, and repair the radiation damage done to the silicon crystal structure by the ion implantation, since these two operations would have required temperatures in excess of the ones survivable by the aluminum gate. Thus his invention provided a proof of principle, but no commercial integrated circuit was ever produced with Bower’s method. A more refractory gate material was needed.

In 1967, John C. Sarace and collaborators at Bell Labs replaced the aluminum gate with an electrode made of vacuum-evaporated amorphous silicon and succeeded in building working self-aligned gate MOS transistors. However, the process, as described, was only a proof of principle, suitable only for the fabrication of discrete transistors and not for integrated circuits; and was not pursued any further by its investigators.

In 1968, the MOS industry was prevalently using aluminum gate transistors with high threshold voltage (HVT) and desired to have a low threshold voltage (LVT) MOS process in order to increase the speed and reduce the power dissipation of MOS integrated circuits. Low threshold voltage transistors with aluminum gate demanded the use of [100] silicon orientation, which however produced too low a threshold voltage for the parasitic MOS transistors (the MOS transistors created when aluminum over the field oxide would bridge two junctions). To increase the parasitic threshold voltage beyond the supply voltage, it was necessary to increase the N-type doping level in selected regions under the field oxide, and this was initially accomplished with the use of a so-called channel-stopper mask, and later with ion implantation.

Development of the silicon-gate technology at Fairchild

The SGT was the first process technology used to fabricate commercial MOS integrated circuits that was later widely adopted by the entire industry in the 1960s. In late 1967, Tom Klein, working at the Fairchild Semiconductor R&D Labs, and reporting to Les Vadasz, realized that the work function difference between heavily P-type doped silicon and N-type silicon was 1.1 volt lower than the work function difference between aluminum and the same N-type silicon. This meant that the threshold voltage of MOS transistors with silicon gate could be 1.1 volt lower than the threshold voltage of MOS transistors with aluminum gate fabricated on the same starting material. Therefore, one could use starting material with [111] silicon orientation and simultaneously achieve both an adequate parasitic threshold voltage and low threshold voltage transistors without the use of a channel-stopper mask or ion implantation under the field oxide. With P-type doped silicon gate it would therefore be possible not only to create self-aligned gate transistors but also a low threshold voltage process by using the same silicon orientation of the high threshold voltage process.

In February 1968, Federico Faggin joined Les Vadasz's group and was put in charge of the development of a low-threshold-voltage, self-aligned gate MOS process technology. Faggin's first task was to develop the precision etching solution for the amorphous silicon gate, and then he created the process architecture and the detailed processing steps to fabricate MOS ICs with silicon gate. He also invented the ‘buried contacts,’ a method to make direct contact between amorphous silicon and silicon junctions, without the use of metal, a technique that allowed a much higher circuit density, particularly for random logic circuits.

After validating and characterizing the process using a test pattern he designed, Faggin made the first working MOS silicon-gate transistors and test structures by April 1968. He then designed the first integrated circuit using silicon gate, the Fairchild 3708, an 8-bit analog multiplexer with decoding logic, that had the same functionality of the Fairchild 3705, a metal-gate production IC that Fairchild Semiconductor had difficulty making on account of its rather stringent specifications.

The availability of the 3708 in July 1968 provided also a platform to further improve the process during the following months, leading to the shipment of the first 3708 samples to customers in October 1968, and making it commercially available to the general market before the end of 1968. During the period, July to October 1968, Faggin added two additional critical steps to the process:

- Replacing the vacuum-evaporated amorphous silicon with poly-crystalline silicon obtained by vapor-phase deposition. This step became necessary since evaporated, amorphous silicon did break where it passed over "steps" in the surface of the oxide.

- The use of phosphorus gettering to soak up the impurities, always present in the transistor, causing reliability problems. Phosphorus gettering allowed to considerably reduce the leakage current and to avoid the threshold voltage drift that still plagued MOS technology with aluminum gate (MOS transistors with aluminum gate were not suitable for phosphorus gettering due to the high temperature required).

With silicon gate, the long-term reliability of MOS transistors soon reached the level of bipolar ICs removing one major obstacle to the wide adoption of MOS technology.

By the end of 1968 the silicon-gate technology had achieved impressive results. Although the 3708 was designed to have approximately the same area as the 3705 to facilitate using the same production tooling as the 3705, it could have been made considerably smaller. Nonetheless, it had superior performance compared with the 3705: it was 5 times faster, it had about 100 times less leakage current, and the on resistance of the large transistors making up the analog switches was 3 times lower.[4]: pp6-7

Commercialization at Intel

The silicon-gate technology (SGT) was adopted by Intel upon its founding (July 1968), and within a few years became the core technology for the fabrication of MOS integrated circuits worldwide, lasting to this day. Intel was also the first company to develop non-volatile memory using floating silicon-gate transistors.

The first memory chip to use silicon-gate technology was the Intel 1101 SRAM (static random-access memory) chip, fabricated in 1968 and demonstrated in 1969.[5] The first commercial single-chip microprocessor, the Intel 4004, was developed by Faggin using his silicon-gate MOS IC technology. Marcian Hoff, Stan Mazor and Masatoshi Shima contributed to the architecture.[6]

Original documents on SGT

- Bower, RW and Dill, RG (1966). "Insulated gate field effect transistors fabricated using the gate as source-drain mask". IEEE International Electron Devices Meeting, 1966

- Faggin, F., Klein, T., and Vadasz, L.: "Insulated Gate Field Effect Transistor Integrated Circuits With Silicon Gates". IEEE International Electron Devices Meeting, Washington D.C, 1968

- US 3475234, Kerwin, Robert E.; Klein, Donald L. & Sarace, John C., "Method for making MIS structures", published 28-10-1969, assigned to Bell Telephone Laboratories Inc.

- Federico Faggin and Thomas Klein.: "A Faster Generation Of MOS Devices With Low Thresholds Is Riding The Crest Of The New Wave, Silicon-Gate IC’s". Cover story on Fairchild 3708, "Electronics" magazine, September 29, 1969.

- Vadasz, L. L.; Grove, A.S.; Rowe, T.A.; Moore, G.E. (October 1969). "Silicon Gate Technology". IEEE Spectrum. pp. 27–35.

- F. Faggin, T. Klein "Silicon Gate Technology", "Solid State Electronics", 1970, Vol. 13, pp. 1125–1144.

- US 3673471, Klein, Thomas & Faggin, Federico, "Doped semiconductor electrodes for MOS type devices", published 1972-06-27, assigned to Fairchild Camera and Instrument Corporation

Patents

The self-aligned gate design was patented in 1969 by the team of Kerwin, Klein, and Sarace.[7] It was independently invented by Robert W. Bower (U.S. 3,472,712, issued October 14, 1969, filed October 27, 1966). The Bell Labs Kerwin et al. patent was not filed until March 27, 1967, several months after R. W. Bower and H. D. Dill had published and presented the first publication of this work at the International Electron Device Meeting, Washington, D.C. in 1966.[8]

In a legal action involving Bower, the Third Circuit Court of Appeals determined that Kerwin, Klein and Sarace were the inventors of the self-aligned silicon gate transistor. On that basis, they were awarded the basic patent US 3,475,234. Actually the self-aligned gate MOSFET was invented by Robert W. Bower U.S. 3,472,712, issued October 14, 1969, Filed October 27, 1966. The Bell Labs Kerwin et al patent 3,475,234 was not filed until March 27, 1967 several months after the R. W. Bower and H. D. Dill Published and presented the first publication of this work entitled INSULATED GATE FIELD EFFECT TRANSISTORS FABRICATED USING THE GATE AS SOURCE-DRAIN MASK at the International Electron Device Meeting, Washington, D.C., 1966. Bower's work described the self-aligned-gate MOSFET, made with both aluminum and polysilicon gates. It used both ion implantation and diffusion to form the source and drain using the gate electrode as the mask to define the source and drain regions. The Bell Labs team attended this meeting of the IEDM in 1966, and they discussed this work with Bower after his presentation in 1966. Bower had first made the self-aligned gate using aluminum as the gate and, before presentation in 1966, made the device using polysilicon as the gate.

The self-aligned gate typically involves ion implantation, another semiconductor process innovation of the 1960s. The histories of ion implantation and self-aligned gates are highly interrelated, as recounted in an in-depth history by R.B. Fair.[9]

The first commercial product using self-aligned silicon-gate technology was the Fairchild 3708 8-bit analog multiplexor, in 1968, designed by Federico Faggin who pioneered several inventions in order to turn the aforementioned non working proofs of concept, into what the industry actually adopted thereafter.[10][11]

Manufacturing process

The importance of self-aligned gates comes in the process used to make them. The process of using the gate oxide as a mask for the source and drain diffusion both simplifies the process and greatly improves the yield.

Process steps

The following are the steps in creating a self-aligned gate: [12]

These steps were first created by Federico Faggin and used in the Silicon Gate Technology process developed at Fairchild Semiconductor in 1968 for the fabrication of the first commercial integrated circuit using it, the Fairchild 3708 [13]

- 1. Wells on the field oxide are etched where the transistors are to be formed. Each well defines the source, drain, and active gate regions of an MOS transistor.

- 2. Using a dry thermal oxidation process, a thin layer (5-200 nm) of gate oxide (SiO2) is grown on the silicon wafer.

- 3. Using a chemical vapor deposition (CVD) process, a layer of polysilicon is grown on top of the gate oxide.

- 4. A layer of photoresist is applied on top of the polysilicon.

- 5. A mask is placed on top of the photoresist and exposed to UV light; this breaks down the photoresist layer in areas where the mask didn't protect it.

- 6. Photoresist is exposed with a specialized developer solution. This is intended to remove the photoresist that was broken down by the UV light.

- 7. The polysilicon and gate oxide that is not covered by photoresist is etched away with a buffered ion etch process. This is usually an acid solution containing hydrofluoric acid.

- 8. The rest of the photoresist is stripped from the silicon wafer. There is now a wafer with polysilicon over the gate oxide, and over the field oxide.

- 9. The thin oxide is etched away exposing the source and drain regions of the transistor, except in the gate region which is protected by the polysilicon gate.

- 10. Using a conventional doping process, or a process called ion-implantation, the source, drain and the polysilicon are doped. The thin oxide under the silicon gate acts as a mask for the doping process. This step is what makes the gate self-aligning. The source and drain regions are automatically properly aligned with the (already in place) gate.

- 11. The wafer is annealed in a high temperature furnace (>800 °C or 1,500 °F). This diffuses the dopant further into the crystal structure to make the source and drain regions and results in the dopant diffusing slightly underneath the gate.

- 12. The process continues with vapor deposition of silicon dioxide to protect the exposed areas, and with all the remaining steps to complete the process.

Notes

References

- Mead, Carver; Conway, Lynn (1991). Introduction to VLSI systems. Addison Wesley Publishing Company. ISBN 978-0-201-04358-7. OCLC 634332043.

- Yanda, Heynes, and Miller (2005). Demystifying Chipmaking. Newnes. pp. 148–149. ISBN 978-0-7506-7760-8.

{{cite book}}: CS1 maint: multiple names: authors list (link) - Orton, John Wilfred (2004). The Story of Semiconductors. OUP Oxford. p. 114. ISBN 978-0-19-853083-1.

- Federico Faggin and Thomas Klein Electronics magazine (September 29, 1969) A Faster Generation Of MOS Devices With Low Thresholds Is Riding The Crest Of The New Wave, Silicon-Gate IC's see pp6-7

- Sah, Chih-Tang (October 1988). "Evolution of the MOS transistor-from conception to VLSI" (PDF). Proceedings of the IEEE. 76 (10): 1280–1326 (1303). doi:10.1109/5.16328. ISSN 0018-9219.

- "1971: Microprocessor Integrates CPU Function onto a Single Chip". The Silicon Engine. Computer History Museum. Retrieved 22 July 2019.

- US 3475234, Kerwin, Robert E.; Klein, Donald L. & Sarace, John C., "Method for making MIS structures", published 28-10-1969, assigned to Bell Telephone Laboratories Inc.

-

Bower, RW & Dill, RG (1966). "Insulated gate field effect transistors fabricated using the gate as source-drain mask". 1966 International Electron Devices Meeting. pp. 102–104. doi:10.1109/IEDM.1966.187724.

{{cite book}}:|journal=ignored (help) - Richard B. Fair (Jan 1998). "History of Some Early Developments in Ion-Implantation Technology Leading to Silicon Transistor Manufacturing". Proc. IEEE. 86 (1): 111–137. doi:10.1109/5.658764.

- John A. N. Lee (1995). International biographical dictionary of computer pioneers, Volume 1995, Part 2. Taylor & Francis US. p. 289. ISBN 978-1-884964-47-3.

- Bo Lojek (2007). History of semiconductor engineering. Springer. p. 359. ISBN 978-3-540-34257-1.

- Streetman, Ben; Banerjee (2006). Solid State Electronic Devices. PHI. pp. 269–27, 313. ISBN 978-81-203-3020-7.

- Faggin, F., Klein, T., and Vadasz, L.: "Insulated Gate Field Effect Transistor Integrated Circuits With Silicon Gates". IEEE International Electron Devices Meeting, Washington D.C, 1968