Segment descriptor

In memory addressing for Intel x86 computer architectures, segment descriptors are a part of the segmentation unit, used for translating a logical address to a linear address. Segment descriptors describe the memory segment referred to in the logical address.[1] The segment descriptor (8 bytes long in 80286 and later) contains the following fields:[2]

- A segment base address

- The segment limit which specifies the segment size

- Access rights byte containing the protection mechanism information

- Control bits

Structure

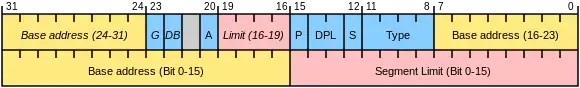

The x86 and x86-64 segment descriptor has the following form:[3]

Where the fields stand for:

- Base Address

- Starting memory address of the segment. Its length is 32 bits and it is created from the lower part bits 16 to 31, and the upper part bits 0 to 7, followed by bits 24 to 31.

- Segment Limit

- Its length is 20 bits and is created from the lower part bits 0 to 15 and the upper part bits 16 to 19. It defines the address of the last accessible data. The length is one more than the value stored here. How exactly this should be interpreted depends on the Granularity bit of the segment descriptor.

- G=Granularity

- If clear, the limit is in units of bytes, with a maximum of 220 bytes. If set, the limit is in units of 4096-byte pages, for a maximum of 232 bytes.

- D/B

- D = Default operand size : If clear, this is a 16-bit code segment; if set, this is a 32-bit segment.

- B = Big: If set, the maximum offset size for a data segment is increased to 32-bit 0xffffffff. Otherwise it's the 16-bit max 0x0000ffff. Essentially the same meaning as "D".

- L=Long

- If set, this is a 64-bit segment (and D must be zero), and code in this segment uses the 64-bit instruction encoding. "L" cannot be set at the same time as "D" aka "B". (Bit 21 in the image)

- AVL=Available

- For software use, not used by hardware (Bit 20 in the image with the label A)

- P=Present

- If clear, a "segment not present" exception is generated on any reference to this segment

- DPL=Descriptor privilege level

- Privilege level (ring) required to access this descriptor

- S=System Segment

- If clear, this is system segment, if 1, this is Code/Data segment.

- Type

- If bit 11 set, this is a code segment descriptor. If clear, this is a data/stack segment descriptor, which has "D" replaced by "B", "C" replaced by "E" and "R" replaced by "W". This is in fact a special case of the 2-bit type field, where the preceding bit 12 cleared as "0" refers to more internal system descriptors, for LDT, LSS, and gates.

- C=Conforming

- Code in this segment may be called from less-privileged levels.

- E=Expand-Down

- If clear, the segment expands from base address up to base+limit. If set, it expands from maximum offset down to limit, a behavior usually used for stacks.

- R=Readable

- If clear, the segment may be executed but not read from.

- W=Writable

- If clear, the data segment may be read but not written to.

- A=Accessed

- This bit is set to 1 by hardware when the segment is accessed, and cleared by software.

References

- Bovet, D.P., & Cesati, M. (2000). Understanding the Linux Kernel (First Edition). O'Reilly & Associates, Inc.

- Tabak, Daniel (1995). Advanced Microprocessors. Mcgraw Hill Publishers. p. 149. ISBN 9780070628434.

- AMD64 Architecture Programmer's Manual Volume 2: System Programming (PDF) (Technical report). 2013. p. 80. Archived from the original (PDF) on 2018-02-18.

- Tabak, Daniel (1991). Advanced Microprocessors. McGraw Hill and Co. ISBN 9780070628076.

- Hall, Douglas. Microprocessors and Interfacing. McGraw Hill Publications.

Further reading

- Robert R. Collins (August 1998). "The Segment Descriptor Cache". Dr Dobb's Journal.

This article is issued from Wikipedia. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.