GE 645

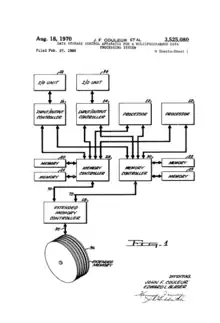

The GE 645 mainframe computer was a development of the GE 635 for use in the Multics project. This was the first computer that implemented a configurable hardware protected memory system. It was designed to satisfy the requirements of Project MAC to develop a platform that would host their proposed next generation time-sharing operating system (Multics) and to meet the requirements of a theorized computer utility.[1] The system was the first truly symmetric multiprocessing machine to use virtual memory, it was also among the first machines to implement what is now know as a translation lookaside buffer.[2][3][4] The foundational patent for which was granted to John Couleur and Edward Glaser.[5]

General Electric initially publicly announced the GE 645 at the Fall Joint Computer Conference[1][3] in November 1965. At a subsequent press conference in December[6][7] of that year it was announced that they would be working towards "broad commercial availability"[8] of the system. However they would subsequently withdraw it from active marketing at the end of 1966.[8] In total at least 6 sites ran GE 645 systems in the period from 1967 to 1975.[9]

System configuration

The basic system configuration consisted of a combination of 4 basic modules[4] these were:

- Processor

- System Controller

- Generalized I/O Controller (GIOC)

- Extended Memory Unit (EMU)

Compared to the rest of the 600 series the 645 did not use the standard IOC's (input/output controllers) for I/O. Nor did it use the DATANET-30 front end processor for communications. Instead both sets of functionality was combined into one unit called a GIOC (Generalized I/O Controller) which provided dedicated channels for both Peripheral (Disc/Tape) and Terminal I/O.[4][10] The GIOC acted as an Active Device and was directly connected to memory via dedicated links to each System Controller that was present in a specific configuration.

| Component | Small | Typical | Large |

|---|---|---|---|

| System Configuration Console | 1 | 1 | 2 |

| Processor | 1 | 2 | 4 |

| GIOC | 1 | 2 | 3 |

| System Controllers

Total Capacity (Words) |

2

128K |

4

256K |

8

1024K |

| Extended Memory Unit

Total capacity (Words) |

1

4096K |

1

4096K |

1

4096K |

| Fixed disc (Words) | 33M | 67M | 134M |

| Magnetic Cards (Words) | -- | 113M | 226M |

| Magnetic tape handlers | 4 | 16 | 32 |

| Printers | 2 | 4 | 6 |

| Card Readers | 1 | 2 | 3 |

| Card Punches | 1 | 2 | 2 |

| Perforated Tape | -- | 1 | 2 |

| Channels for TTY's | 64 | 192 | 384 |

| Channels for voice-grade communication lines

for remote terminals such as such as DATANET-760 / GE-115 |

-- | 12 | 18 |

Architecture

Processor Modes

The GE-645 has two modes of Instruction Execution (Master and Slave) inherited from the GE-635, however it also adds another dimension by having two modes of memory addressing (Absolute and Appending). When the process is executing in Absolute Mode addressing is limited to 218 words of memory and any instructions are executed in Master mode. In comparison Append Mode calculates the address using "Appending Words" with an address space of 224 words and with instruction execution occurring in either Master or Slave modes.[11]

Slave Mode

By default this is normal mode that the processor should be executing in at any point in time. Nearly all instructions will run in this mode aside from a small set of privileged instructions which cannot execute in this mode. Execution of such instructions will trigger an illegal procedure fault, also the ability to inhibit interrupts (bit 28 of instruction word) is forbidden. Format of instruction addresses is via the Appending Process.

Master Mode

In this mode the processor can execute all instructions and is able to inhibit interrupts while doing so. Like in Slave mode the default form of address formation is via the Appending Process.

Absolute Mode

All instructions can be executed in this mode and full access is given to any privileged features of the hardware. Interrupts can be inhibited and instruction fetching is limited to a 218 (18-bit) absolute address thus restricting the processor to only been able to access the lower 256 KW of physical core memory. The processor will switch to this mode in the event of a fault or interrupt and will remain in it until it executes transfer instruction whose operand address has been obtained via the appending process.

Appending Mode

By default this is normal mode of Memory addressing, both Master and Slave modes normally operate in this mode. Indirect words and operands are accessed via Appending Mechanism via the process of placing a 1 in bit 29 of the executed instruction. Effective addresses are thus either added to a base address, or the offset is linked to the base address.

| Fuctions | Mode | ||

|---|---|---|---|

| Slave | Master | Absolute | |

| Privileged instructions | No | Yes | Yes |

| Interrupt inhibit (bit 28 of instruction word) | No | Yes | Yes |

| Address for Instruction fetch | Appending | Appending | Absolute |

| Address for Operand fetch | Appending | Appending | Controlled by Bit 29 of instruction word |

| Restriction of access to other segments or pages | Some | Some (less restrictive than slave) | N/A |

Functional Units

The 645 processor was divided into four major functional units these were:[11]

- Appending Unit:

- Controls data I/O from memory

- Controls memory selection and interleave

- Carries out Memory appending

- Control fault recognition

- Does power on/off sequencing

- Associative Memory Unit:

- Consists of Associative Memory made up of 16 x 60-bit Registers [12]

- Registers point to most recently used segment (Segment Descriptor Word) or most recently used Page (Page Table)

- Performs the fuction of what would now be classed as a TLB.

- Control Unit:

- Performs all control fuctions

- Performs Address modification

- Controls the processor mode (master, slave, absolute)

- Interrupt recognition/handling

- Opcode decoding

- Operations Unit:

- Performs fractional and integer divisions and multiplications.

- Performs automatic alignment of floating-point numbers for addition and subtraction.

- Performs inverted divisions on floating-point numbers.

- Performs automatic normalization of floating-point resultants.

- Performs shifts.

- Performs indicator register loading and storing.

- Performs timer register loading and decrementing.

One of the key differences from the GE 635 was the addition of "appending unit" (APU) which was used to implement a hybrid "Paged Segmentation" model of virtual memory. The APU was also used to implement a single-level store which is one of the fundamental abstraction that Multics is built around. The instruction format was also extended with the previously unused bit 29 controlling whether the operand address of an instruction used an 18-bit format (bit 29 = 0) or one that was made up of a 3-bit Base Register address with a 15-bit offset (bit 29 = 1). [4][11]

GE-645 Instruction Format

0 0 0 1 1 2 2 2 3 3

0 2 3 7 8 6 7 9 0 5

+---+---------------+---------+---+------+

|BR | ADDRESS | OPCODE |UIB| TAG |

+---+---------------+---------+---+------+

Field Name Size Purpose

---------- ------- -------

BR 3 bits base register; 0-7

ADDRESS 15 bits word address; 0-32767 (32KW)

OPCODE 9 bits instruction opcode

U 1 bit unused

I 1 bit interrupt inhibit flag

B 1 bit 0=no base register (GE-635 format)

1=base register (GE-645 format)

TAG 6 bits index/indirect type

History

The original CTSS was implemented on a modified IBM 7094 with two banks of memory and bank-switching between user and supervisor mode, i.e. programs running in the A-core memory bank had access to instructions that programs running in the B-core bank did not.[13] While the GE 645 hardware was been designed and debugged in Phoenix a system was put in place where a GE 635 could be used to run a simulator known as the 6.36[14] of so that development and checkout of Multics could occur in parallel. This process involved creating a tape on the CTSS system which would be inputted to GECOS on the 635 system in MIT so that it would run under the 6.36 simulator, the resulting output would be carried back via tape to CTSS for debugging/analysis.[15] This simulated environment was replaced by the first 645 hardware in 1967. The GECOS operating system was fully replaced by Multics in 1969 with the Multics supervisor (master mode now known as kernel mode)[3][16]

A later generation in the form of the 645F (F for follow-on) wasn't completed by the time the division was sold to Honeywell, and became known as the Honeywell 6180. The original access control mechanism of the GE/Honeywell 645 were found inadequate for high speed trapping of access instructions and the re-implementation in the 6180 solved those problems.[17] The bulk of these computers running time-sharing on Multics were installed at the NSA and similar governmental sites. Their usage was limited by the extreme security measures and had limited impact on subsequent systems, other than the protection ring.[18]

The hardware protection introduced on this computer and modified on the 6180 was later implemented in the Intel 286 computer processor as a four-layer protection ring, but four rings was found to be too cumbersome to program and too slow to operate. Protection ring architecture is now used only to protect kernel mode from user mode code just as it was in the original use of the 645.[3]

See also

Further reading

- Organick, Elliott Irving (1972). The Multics system; an examination of its structure. Cambridge, MIT Press. ISBN 978-0-262-15012-5. Retrieved 22 October 2023.

- Watson, Richard W. (1970). Timesharing system design concepts. New York [usw], Düsseldorf: McGraw-Hill. ISBN 978-0070684652. Retrieved 22 October 2023.

- Donovan, John J. (1972). Systems programming. McGraw-Hill. ISBN 978-0-07-017603-4. Retrieved 22 October 2023.

- Kaisler, Stephen H. (22 October 2020). Mainframe Computer Systems: The General Electric Corporation. Cambridge Scholars Publishing. ISBN 978-1-5275-6116-8. Retrieved 22 October 2023.

References

- Corbató, F. J.; Vyssotsky, V. A. (30 November 1965). "Introduction and overview of the multics system". Proceedings of the November 30--December 1, 1965, fall joint computer conference, Part I on XX - AFIPS '65 (Fall, part I). Association for Computing Machinery. pp. 185–196. doi:10.1145/1463891.1463912. ISBN 9781450378857. S2CID 11197018.

- John Couleur (Winter 1995). "The Core of the Black Canyon Computer Corporation" (PDF). IEEE Annals of the History of Computing. 17 (4): 56–60. doi:10.1109/85.477436.

- Glaser, E. L.; Couleur, J. F.; Oliver, G. A. (30 November 1965). "System Design of a Computer for Time Sharing Applications". Proceedings of the November 30--December 1, 1965, fall joint computer conference, Part I on XX - AFIPS '65 (Fall, part I). Association for Computing Machinery. pp. 197–202. doi:10.1145/1463891.1463913. ISBN 9781450378857. S2CID 15819355.

- "GE-645 System Manual" (PDF). General Electric. January 1968. pp. 18, 22. Retrieved 26 September 2023.

- US patent 3412382, COULEUR JOHN F & GLASER EDWARD L, "Shared-access data processing system", assigned to Massachusetts Institute of Technology

- Smith, William D. (2 December 1965). "A New Computer Developed at G.E." The New York Times. Retrieved 20 October 2023.

- "GE-645 Timesharing System". Digital Computer Journal. Office of Naval Research - Mathematics Science Division. 18 (2): 5–6.

- "US vs IBM_Exhibit 14971 - Historical Narrative The 1960's" (PDF). pp. 434, 510. Retrieved 21 October 2023.

- "Multics Site Timeline". multicians.org. Retrieved 21 October 2023.

- Ossanna, J. F.; Mikus, L. E.; Dunten, S. D. (30 November 1965). "Communications and input/Output switching in a multiplex computing system". Proceedings of the November 30--December 1, 1965, fall joint computer conference, Part I on XX - AFIPS '65 (Fall, part I). Association for Computing Machinery. pp. 231–241. doi:10.1145/1463891.1463916. S2CID 15847853.

- "MODEL 645 PROCESSOR REFERENCE MANUAL" (PDF). Honeywell Information Systems Inc. May 1972. Retrieved 26 September 2023.

- Schroeder, Michael D. (1971). "Performance of the GE-645 Associative Memory While Multics is in Operation". Proceedings of the SIGOPS workshop on System performance evaluation. Association for Computing Machinery. pp. 227–245. doi:10.1145/800024.808361. ISBN 9781450373821. S2CID 44850627.

- Crisman, P.A., ed. (December 31, 1969). "The Compatible Time-Sharing System, A Programmer's Guide" (PDF). The M.I.T Computation Center. Retrieved March 10, 2022.

- "The GE-635s at Project MAC and BTL". multicians.org. Retrieved 19 October 2023.

- "Project MAC Progress Report III, 1966-67" (PDF). Archived from the original (PDF) on June 4, 2016.

- "Project MAC Progress Report V, 1966-68" (PDF). Archived from the original (PDF) on June 4, 2016.

- Michael D. Schroeder and Jerome H. Saltzer. "A Hardware Architecture for Implementing Protection Rings". Retrieved 27 September 2012.

- Donald A. MacKenzie (2001). Mechanizing Proof: Computing, Risk and Trust. The MIT Press. ISBN 0-262-13393-8.